NEWS

【EDSFレポート】ケイデンス、インプリ工程を分散対応/CPFテープアウト100件超

Electronics Design and Solution Fair 2009に出展していたケイデンスのブースレポート。

今回のケイデンスの展示の目玉は?と訊ねてまず返ってきたのは、新しくなったデジタルインプリメント環境「Encounter Digital Implementation System(EDI)」。

日本ケイデンス、プロダクト・マーケティング部ディレクターの田中氏によると、「EDI」は従来のインプリメント環境「SoC Encounter」の後継製品で、ツール内部のデータ構造やメモリ使用の改良を施しパフォーマンスを強化。ツールのアーキテクチャ変更により、配置配線だけでなくインプリ工程の殆どをパラレルに処理できるようになった。これにより、より大規模なデザインに対応可能に。既に「SoC Encounter」からの移行が進んでいるという「EDI」の分散処理は、単一筐体内の複数CPUへの分散と、ネットワーク上のCPUへの分散の両方に対応しているという。

また、田中氏によると、「EDI」にSDC生成・検証ツール「Encounter Conformal Constraint Designer」を組み合わせて使うとそのシナジー効果は絶大。設計制約における冗長性を排除し制約の最適化が実現できるため、レイアウト作業が非常に楽になるという。ちなみに「Encounter Conformal Constraint Designer」は最近STARCが採用済み。

また、田中氏によると、「EDI」にSDC生成・検証ツール「Encounter Conformal Constraint Designer」を組み合わせて使うとそのシナジー効果は絶大。設計制約における冗長性を排除し制約の最適化が実現できるため、レイアウト作業が非常に楽になるという。ちなみに「Encounter Conformal Constraint Designer」は最近STARCが採用済み。

尚、Conformalシリーズでは新たに入手した情報が一つ。ごく最近リリースされたばかりの低消費電力設計用の検証ツール「Conformal Low Power」に、Powerフォーマット「CPF」を生成する新機能が追加されたようで、同機能を用いればPower制約に関するCPF記述をGUI上の入力で自動生成できると聞いた。CPFを用いた低電力デザインのテープアウト実績は既にワールドワイドで100件超。「CPF」のユーザビリティが高まれば、更に実績は増えるだろう。

その他、ケイデンスブースで目に付いたのは、IPポータルサイト「ChipEstimate.com」の展示。同サイトは主にセットメーカーのユーザーを対象にIPの選択を支援するもので、チップ設計の見積ツールをサイト上で無償で提供している。IDE向けには、大量な社内IP資産をターゲットとしたチップ・プランニング・システムをカスタム開発しているらしい。

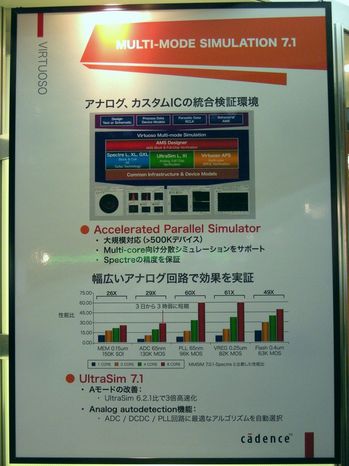

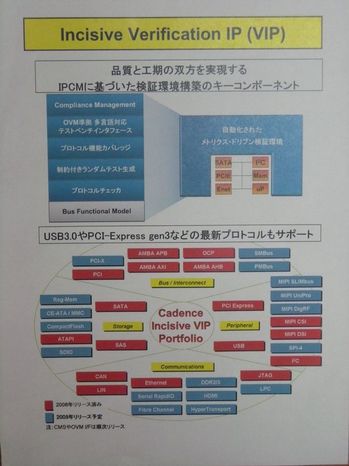

その他のトピックスとしては、昨年リリースした動作合成ツール「C to Silicon Compiler」は出だし上々で、既に初期顧客の日立/ルネサス以外にも国内ユーザーが存在している様子。検証関連ではOVMの普及に伴い一気に検証IPのラインナップを拡張。次世代回路シミュレータ「Virtuoso Accelerated Parallel Simulator」は、分散シミュレーションで30?60倍の処理速度を実現(8CPU利用時)可能という。

関連記事:

関連記事:

STマイクロ、40/32nmフロー向けにケイデンスの新型インプリメント環境を採用

ケイデンスの動作合成「C-to-Silicon Compiler」がFPGA向けの合成をサポート

STARC、STARCAD-CEL設計フローにケイデンスのSDC生成・検証ツールを認定

|ページの先頭へ|