HOT TOPIX

SNUG Japan 2017 HAPSを用いて3時間要するシミュレーションを10分で完了:コニカミノルタの事例

2017年9月8日、日本シノプシスは都内のホテルでプライベート・セミナー「SNUG Japan 2017」を開催した。

ここでは同イベントで行われたコニカミノルタの講演「プロトタイピングシステムHAPS-80を用いた、システム検証環境構築の紹介」についてレポートする。

講演者は、コニカミノルタ株式会社 情報機器開発本部 システムプラットフォーム開発センター 第二プラットフォーム開発部 高橋 一誠氏である。

コニカミノルタ 高橋氏

高橋氏は、MFP(プリンタ複合機)の画像制御ASICと画像制御ファームウェアの開発を担当する部署に所属しており、ASICとFWの品質確保を目的にES入手前のHW/SW協調検証に取り組んでいる。

同社では、既にSynopsysのバーチャル・プロトタイピング環境「Virtualizer」で作成したバーチャル・プラットフォーム(以下、VPF)とエミュレーション環境「Zebu」を組み合わせたHW/SW協調検証を構築しており、ES入手前のHW/SW検証において一定の成果を上げていた。そんな背景の中で高橋氏が目指したのは、更なる検証の高速化とVPFの代替え手段の確保、そして検証範囲の拡大だった。

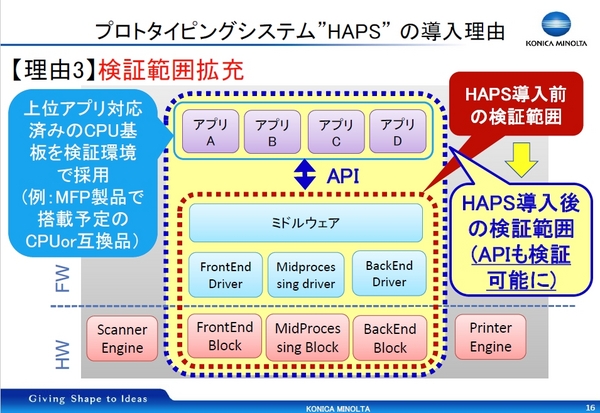

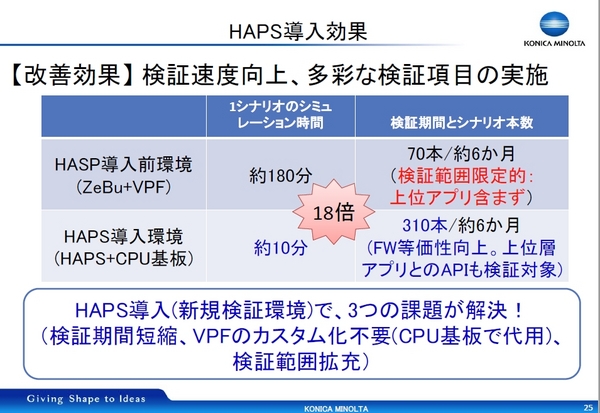

高橋氏によると、既存の協調検証環境では実原稿サイズ(A4サイズ)の画像を用いたシミュレーションに要する時間は1テスト当たり約3時間。検証項目の拡充など検証品質の更なる向上を考えるとより高速な検証環境が欲しくなる。また、CPUモデルを実装するVPFの構築準備(カスタム)・導入に時間がかかるため、検証開始の遅延リスクを回避する別の手段を考える必要もあった。更に既存の検証環境では、環境構築上の問題からソフトウェアの検証範囲がミドルウェアまでとなっていたため、上位のアプリを含んだ協調検証を実現したかった。

これらの要求から浮かび上がった解決策がSynopsysのFPGAベース・プロトタイピング環境「HAPS」導入だった。高橋氏は「HAPS」を用いることで以下のような効果が得られると考えた。

・検証速度の向上:対Zebu比で約8倍 例)A4サイズ検証に要する3時間が22分に

・VPFの代替え手段の確保:HAPSにメーカー製のCPU基板を接続可能

・検証範囲の拡大:メーカー製CPUの利用により上位アプリとのAPIも検証可能に

そして実際に「HAPS」シリーズの最上位品「HAPS-80」を導入した同社は、ES入手後の試作機即動作を目指して、「HAPS-80」、メーカー製CPU、各種独自基板から成る検証環境を構築した。独自基板とはスキャナ、エンジン、操作パネルなどMFP特有のI/Fモジュールと同社独自のペリフェラルで、これらを用意・接続する事でMFPの主要なソフトウェア・シーケンスを検証できる検証環境を実現できた。(もちろん画像処理回路はHAPSにインプリ)

実際に構築した「HAPS-80」ベースの協調検証環境の導入効果は下記スライドの通り。検証速度の大幅な向上をはじめ、見込んでいた導入効果を全て実現する事に成功した。具体的な成果としては、既存のVPUと「Zebu」による協調検証環境で検出したバグ以外に、新たなバグを計36件(ソフト34件、ハード2件)検出したという。

高橋氏は、「HAPS」ベースの協調検証環境を活用することで実機評価の一部を前倒しできるとし、それは追加検証、そして品質向上に繋がるとコメント。既存環境との比較については、「Zebu」と「HAPS」どちらが優れているという話ではなく、両製品のそれぞれの特徴を活かして適材適所使い分ける事が大事であると語った。

※画像は全て高橋氏の公開講演データ

|ページの先頭へ|