HOT TOPIX

【DAC50】第50回Design Automation Conference-今年のDACは。。

2013年6月2日-6日、米テキサス州オースティンで第50回Design Automation Conferenceが開催された。

今年のDACは50週年目にして初となるオースティン開催で、展示会への出展企業数は若干減ったものの、来場者数は体感的に昨年同等もしくは昨年より微増といったところ。展示会のスペースは非常にコンパクトになったせいか、会期を通じて一定の人口密度が保たれており、狭いながらも活気ある展示会場という感じであった。(主催者による来場者数の公式発表は未だ。)

論文の投稿数は昨年同等の約700本という事で、うち採択された158本の論文がテクニカル・セッションで披露されたほか、「Designer Track」と呼ぶ56件のユーザー事例のセッションや100件近いポスター・セッションが実施された。カンファレンス最終日に発表された、DAC50のBest PaperおよびDesigner Track Best Paperは以下の通り。尚、「Designer Track」では、日本から東芝のチームがESL関連とフィジカル設計関連で2件、NTTのチームがHLS(高位合成)関連で1件の発表を行なっていた。

・Best Paper

Zhuo Feng - Michigan Technological Univ

・Designer Track Best Paper

Udo Krautz - IBM Systems and Technology Groupほか

今年はDAC50周年という事で、様々なイベント、セッションを通じて業界のこれまでを振り返り今後を探る話題が多かった。キーノートでも同様で、初日に登壇したFreescale社のCEO Gregg Lowe氏は、IoT(Internet of Things)の世界は既にはじまっており、爆発的に増加する組込みプロセッサの更なる小型化、低消費電力化は挑戦であると同時にビジネス・チャンスと語り、2日目に登壇したNationai InstrumentsのCEO James Truchard氏は、複雑化・大規模化の進む今後のSoC開発はシステム・レベルのプラットフォーム・ベース設計が必要不可欠と説き、これからはソフト・エンジニアもハード・エンジニアもシステム・レベル・デザインを知らないといけないと語った。

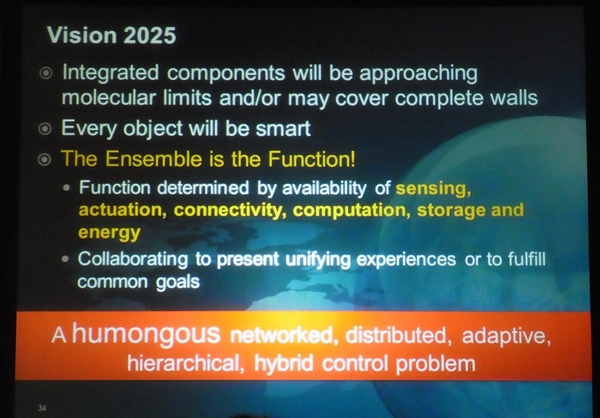

3日目に登壇したSamsungのLSI事業部トップのNamSung (Stephen) Woo氏は、スマホを例に未だシステムを実現するために1ダース以上のチップを必要としているとし、本当のSoCの実現をはじめ未来のデバイスを創るためには、プロセス、EDA、マニファクチャリング、ソフト、マーケティング、各分野の協力が必要と述べた。最終日に登壇したCadenceのファウンダーでもあるUCバークレーのAlberto L. Sangiovanni-Vincentelli教授は、来るべき2025年の世界はシステムが巨大化し、もはや機能として単一のデバイスは無くなり、センサー、アクチュエーター、ネットワーク、ストレージ、コンピューティングなど様々なものがアンサンブルで機能を実現すると指摘。複雑かつ巨大なシステムを扱うためには、プラットフォーム・ベースのシステムとシステムの協調設計など新たな設計パラダイムが必要で、EDAは重要なポジションにいると語った。

※画像はAlberto L. Sangiovanni-Vincentelli教授の講演資料

尚、今年は各キーノートに前に、EDAトップ3のエグゼクティブとEDACチェアマンが「VISIONARY TALK」という10分間の講演を披露。EDAトップ3のエグゼクティブ各者がEDA市場の明るい展望とエレクトロニクス産業におけるEDA技術の重要性を説く一方で、最終日に登壇したJasper Design Automation CEO兼EDACチェアマンのKathryn Kranen氏は、EDA産業の現状を「大手3社が支配するエイジング産業だ」と表現し、イノベーションは小さな会社から生まれるものだが、現状小さな会社は大手のEDAツールを買うことが出来ないと問題意識を提起。イノベーションを生み出すには、デザイン・チームの能力とEDAツールのエコシステムが鍵となると主張した。

例年、DACにおけるEDA業界の動向を掴むのに欠かせないのが業界のアナリストGary Smith氏の講演だが、今年も同氏が推したのはやはりESLツールだった。Gary Smith EDA社が公開した「WHAT TO SEE @ DAC 2013」にリストアップされた34社の製品のうち13製品がESL関連で、中でもAtrentaやDuologが提供するシリコン・バーチャル・プロトタイピング・ツールは、大規模IPベース設計において重要であるとした。

※中央の男性がGary Smith氏、講演前に恒例の一曲。

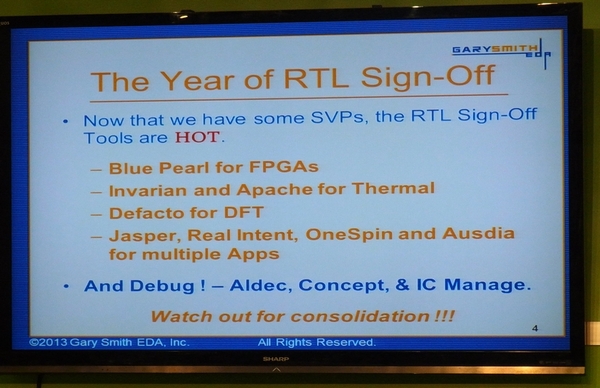

また、Gary Smith氏は今年は「RTLサインオフの年」と語り、パワー情報を含んだゴールデンRTLを如何に作るかが重要であり、RTLサインオフのためのツールも揃ってきたと、FPGA設計向けデザイン解析のBlue Pearl、サーマル解析のInvarian、Apache、DFTツールのDefacto、フォーマル検証ツールのJasper、Real Intent、OneSpin、Ausidaなどを紹介した。

フロントエンドのツール以外では、大手ツールに対抗し実績を上げている企業として配置配線ツールのATopTechとアナログSPICEシミュレータのBerkeley Design Automationを紹介。更に先端プロセスのばらつき解析で重要なポジションを獲得しているSolid Design Automation、DFYツールのスタートアップProPlus Design Solutions、DRCデック・コンパイラのスタートアップSage Design Automationらも注目企業として紹介した。

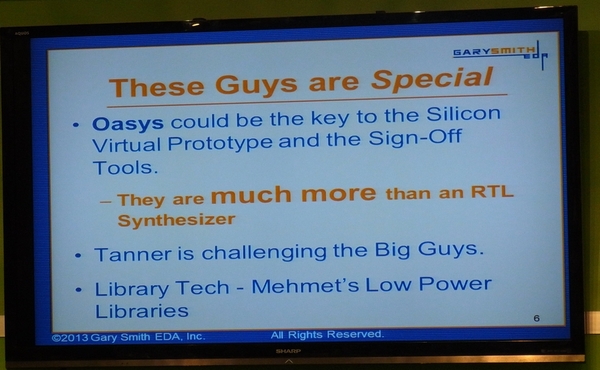

最後にシリコン・バーチャル・プロトタイプならびにRTLサインオフの鍵となる最も注目すべき企業として、フィジカル考慮の論理合成ツールを手掛けるOasys Design Automationを紹介、コストパフォーマンスの高さで大手に挑むTanner EDA、ローパワー・ライブラリを手掛けるLibrary Technologiesも要注目企業として挙げた。

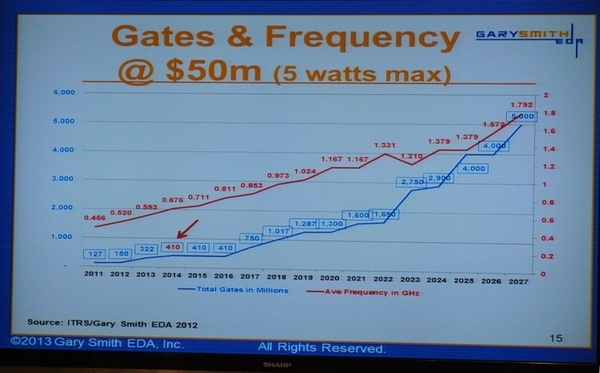

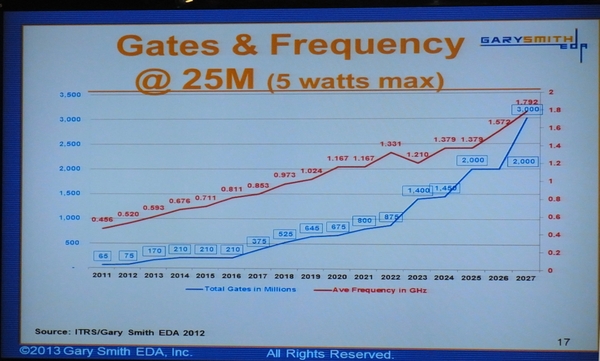

デザインのトレンドについては、もはやパフォーマンス=動作周波数ではなく、パフォーマンス=パワー+レイテンシとなったと語り、ユーザー視点からするとパフォーマンスは利用できるアプリケーションの数、すなわちゲート数になってきているとした。Smith氏はその上で、消費電力の制約を最大5Wとした場合、ITRSのロードマップをベースに将来利用できるゲート数を分析すると、その規模は2027年には約127億ゲートに到達、平均動作周波数約1.8GHzの回路が実現できるとし、更に設計コストを5000万ドルとすると利用できるゲート数は50億ゲート程度、設計コストを2500万ドルとすると30億ゲートで同等の動作周波数の回路を実現可能とし、これは半導体スタートアップでも許容出来る悪くない数字であるとした。

尚、Smith氏は、こうした大規模デザインを実現するためにはESL技術が必要不可欠と持論を展開したが、実際にはESLフローは発展しつつあるが、RTL設計者がソフトウェアを理解できないため期待通りにESLが浸透していないとコメント、ESLの普及にはソフトが分かる若いエンジニアに期待するとした。またESLによってEDAを組込みソフト開発分野へ拡張できるとし、そのために重要なのはモデルであり、アーキテクトとソフトウェア開発者が必要なモデルを持っているのは我々ハードウェア設計者、ツールは渡してもモデルは渡してはいけないと力説した。

展示会場全体を見渡して、大手3社以外で目立っていたのは、パートナーが多数集うARMのブース、常にステージ・プレゼンテーションで人を集めていたTSMCブース、Mentorが自社ブースとは別に構えていたVerification Academyのブースなど、またIC ManageやATopTech、Forte、Calypto、Atrentaといった業績好調な中堅ベンダらがブースの規模を拡張しており、それなりの存在感を示していたのも印象的だった。

個別の各EDAベンダのブース展示については、別途レポート記事を掲載します。

|ページの先頭へ|