HOT TOPIX

2012年のEDA業界を振り返る、今年の話題10選

|コメント(1) |

今年も残すところあと僅かとなりました。言うまでもなく今年は、日本のエレクトロニクス業界にとって苦境の1年となりましたが、ワールドワイドのEDA業界にとっては、大きな成長の1年となりました。

ここでは、今年の締め括りとして、EDA業界を取り巻くこの1年の出来事を振り返り、そのトレンドをまとめてみたいと思います。

■EDA大手3社が軒並み業績アップ

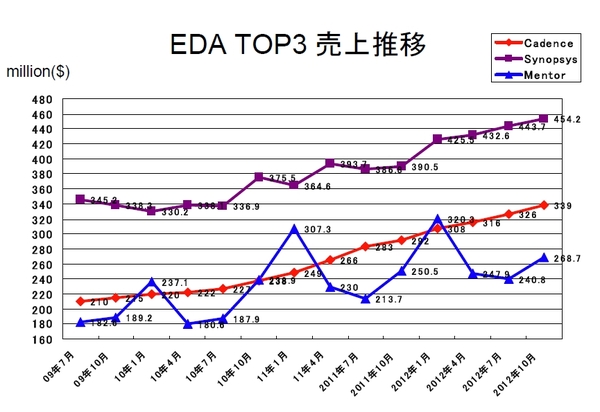

EDA市場の6割以上を占めるSynopsys,Cadence,Mentorの大手3社の勢いが今年更に増した。同3社は、公表している直近の4四半期の全てにおいて売上前年比増を達成し、3社揃って年間売り上げ記録を更新する勢いを見せている。現時点ではSynopsys,Mentorが10月まで、Cadenceは9月までの売上しか公表されていないが、各社が過去最高売上を叩き出すのはほぼ間違いの無い状況と言える。

この大手3社好調の原動力の一つとなっているのは、先端プロセス向けデザインへの投資で、Intel,Samsungなど大口顧客によるツール導入が拡大したほか、28nmプロセスの立ち上がりに伴うハイエンド・チップのリリース・ラッシュで、ファブレス各社のニーズも大きく伸びたようだ。

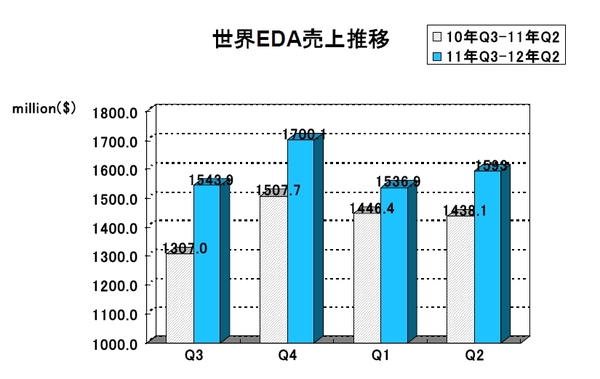

また、大手3社の勢いは当然ながら全EDA市場の規模を拡大しており、EDAの業界団体EDACが公表している世界EDA売上統計データによると、今年に入り既にQ1(1-3月)、Q2(4-6月)と前年比増を記録。現時点で9四半期連続で売上前年増を記録しており、2012年上半期の累計売上額は約31億3000万ドル、前年比8.5%増となっている。仮に昨年と同様のペースで下半期の売上が推移すると、2012年の世界EDA売上は66億5000万ドルに達する。

EDA大手3社の業績は以下の通り。

・Synopsys

9四半期連続で売上前年比増を記録、2012会計年度(2011年11月-2012年10月)の売上合計は17億5600万ドルで同社過去最高を更新。

・Cadence

11四半期連続で売上前年比増を記録、2012年会計年度(2012年1月-12月)の売上合計は13億1500-13億2500ドルの見込み。

・Mentor 10四半期連続で売上前年比増を記録、2013会計年度(2012年2月-2013年1月)は売上11億ドル超の見込み。

※Cadenceは、会計上の四半期を1-3月,4-6月,7-9月,10-11月と設定しているが、グラフ上の数値は、MentorおよびSynopsysの四半期設定である2-4月,5-7月,8-10月,11-1月に合わせている。

公表されている直近四半期の各社の売上は以下の通り。

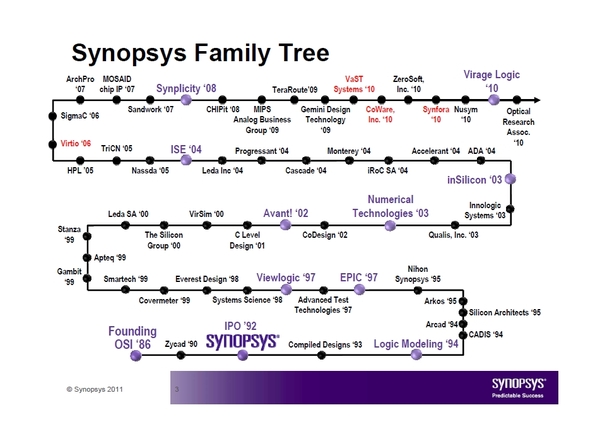

■Synopsysの買収攻勢

業界首位を独走するSynopsysの企業買収攻勢が今年再び活発となった。

昨年発表したMagmaの買収を今年2月に完了、12月にはSpringSoftの買収を完了し、今年だけで2件総額9億ドル超の大型買収を済ませたほか、エミュレーター製品の老舗EVEも買収し、名だたる中堅EDAベンダが一気にSynopsysに吸収された。また図研の子会社インベンチュアをはじめ、Synopsysは幅広い分野に触手を伸ばし、今年1年間で公表された同社の企業買収は計7件に上った。

以前から次なるSynopsysの買収候補と噂されるESLからフロントエンド寄りの中堅EDAベンダが幾つかあるが、それら候補以外にもソグラフィ最適化、歩留まり最適化、統計的バラつき解析など、バックエンド寄りで独自のフォーカス分野を持ち、TSMCやGF等のファウンドリとの実績もある小規模EDAベンダが買収される可能性もあるだろう。

ちなみに、Synopsysによる企業買収の累計件数は、今年の7件を含め計62件となっている。(※事業部門買収や投資を除く)

【この1年間のSynopsysの買収実績】

1月:ExpertIOを買収、買収額非公開

2月:インベンチュア株式会社を買収、買収額非公開

2月:Magma Design Automationを買収、買収額約5億2300万ドル

5月:RSoft Design Groupを買収、買収額非公開

7月:Ciranovaを買収、買収額非公開

10月:Eveを買収、買収額非公開

12月:SpringSoftを買収、買収額約4億1700万ドル

※画像はSynopsys買収の歴史。SystemC Japan 2011における日本シノプシスの発表資料抜粋

■進化を遂げたFPGA設計環境

今年はAltera,Xilinx,2大FPGAベンダの設計環境が大きく進化を遂げた一年となった。

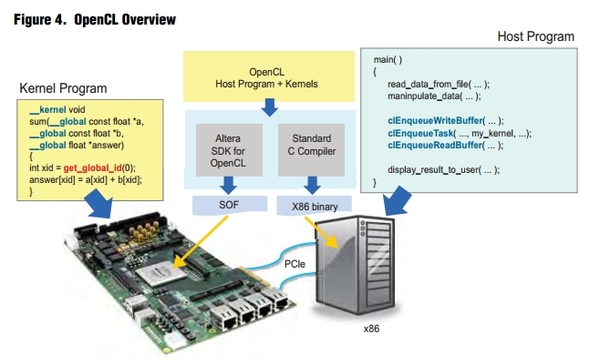

Alteraは、業界初となるOpenCLを用いたFPGAベース・システム開発用のSDKを発表。C言語ベースのOpenCLからのFPGA設計を実現した。このアプローチは、CPUとFPGAで構成されるヘテロジニアス・システムの開発をターゲットとしたもので、ソフトウェア開発者によるFPGA設計を可能とするだけでなく、FPGA利用による容易なシステム性能の向上と消費電力の削減を実現する。

このAlteraの打ち出したOpenCLからの設計フローは、2013年から量産出荷されるARM搭載FPGA「SoC FPGA」の開発を見据えたもので、Alteraは同SDK以外にもARMと共同開発した「ARM DS-5 アルテラ・エディション・ツールキット」を投入し、この1年で「SoC FPGA」向けの開発環境を固めた。また、Alteraの専用設計環境「Quartus II」もバージョンアップされ、処理の高速化が施されたほか、最新の28nm FPGAや「SoC FPGA」と合わせてOpenCLからの設計フローもサポートされた。

※画像はAltera社ホワイト・ペーパーからの抜粋

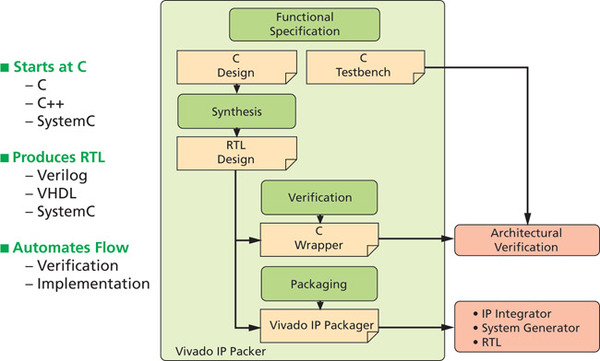

Xilinxは、次の10年を見据えた設計環境として新たな専用設計環境「Vivado」をリリースした。「Vivado」は、論理合成、配置配線、シミュレーターと各エンジン全てが既存の環境「ISE」から刷新された新しい設計環境で、論理合成ならびに配置配線のパフォーマンスが大幅に強化されRTLからのインプリメントの生産性が数倍レベルで高められた。

更に「Vivado」は、業界初となる高位合成エンジンの搭載を実現。「Vivado」の高位合成エンジンは、Xilinxが2011年に買収したAutoESL社の高位合成ツールを基にしたもので、C/C++/SystemC言語からの高位合成が可能。デザイナーはVerilog/VHDLに加え、C言語ベースでXilinxのFPGAを設計出来るようになっただけでなく、C言語ベースのモデルを利用した高速なシステム・シミュレーションが可能となった。Xilinxは更に今後のロードマップとして、IP-XACTの技術を活用したシステムレベルのIPインテグレーション機能「IP Integrator」の提供などを掲げており、FPGA設計向けESL環境の更なる充実を図る計画。その背景には、Alteraに先行する形で既に量産体制に入ったARM搭載FPGA「Zynq-7000」の存在がある。

※画像はXilinx社ホワイト・パーパーからの抜粋

■ARM,ARM,ARM,,,

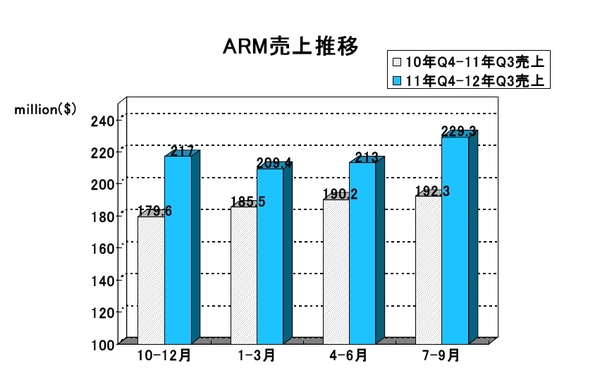

ARMの快進撃が止まらない。今年、ARM搭載チップの出荷数は9年前の4億5000万個から約16倍の80億個を超える見込みで、急成長を遂げたスマートフォン、タブレット市場はまさにARMの独壇場と化した。手を緩めないARMは、今年10月に更に次世代のARMコア「Cortex-A57」と「Cortex-A53」を発表し、モバイル市場だけでなくサーバーや通信インフラなど儲かる新たな市場の開拓に意気込みを示した。

業績としては、2010会計年度Q1(1-3月)以来、11四半期連続で売上前年比増を達成しており、直近の2012会計年度Q3(7-9月)の売上は前年比18%増の2億2930万ドル、このまま行くと2012会計年度は前年比15%増近い9億ドルに達する見込みで、今年の新規プロセッサ・ライセンスの獲得数は100件近くになる計算。同社のライセンシーはワールドワイドで300社を数えるという話だ。

その大きな影響力から1000社を超えるパートナー企業と巨大なエコシステムを築いてるARMだが、今最も力を入れて連携しているのが先端プロセスでのチップ実現に欠かせないパートナーとなる半導体ファウンドリならびにEDA大手各社で、今年もEDAの世界ではARMとのパートナーシップ関連の話題が多く目についた。代表的なニュースは以下の通り。

また、ARM関連のEDAツールとしては、ESLツールの対応が活発でこの1年間で以下のようなニュースがあった。

尚、ARMはハイエンドのプロセッサ・コアの新たな差別化要素となりうる、モバイル決済向けセキュリティの合弁事業「Trustonic」を立ち上げたり、超低消費電力プロセッサ・コアのニーズが期待できる来たるべくIoT(Internet of Things)の世界を睨み、IoTに関する標準化団体「Weightless SIG」に参画したりと、この1年間で新たな動きも見せていた。

■14nmが見えてきた先端プロセス

プロセスの微細化は現在Intelの22nmを筆頭に、ファンドリ各社の28nmプロセスが立ち上がりはじめている。28nmプロセスにおけるプレイヤーとしては、先頭を走るTSMCの他に、UMC、GlobalFoundries、Samsung、STMicroelectronics、SMICが挙げられるが、ロードマップは既にその先の20/16/14nmプロセスの開発が示されており、ファウンドリ各社の動きは現時点で大きく以下のような状況となっている。

■IP Wars

IPビジネスを拡大させる業界首位Synopsysと2位Cadence、今年は両社のIP市場における競争がより顕著化した1年でもあった。買収した旧Denali社のビジネス基盤をベースにメモリおよびストレージ向けIPで強みを見せるCadenceに対し、SynopsysはプロセッサやアナログIPなども取り揃える豊富なラインナップを強みとしており、今年も更にIPラインナップを拡充、検証IPに関してはそのアーキテクチャの刷新を図った。ここ最近は、各種インタフェース規格関連のIP、ならびにARMのAMBAバス関連のIP分野で両社が火花を散らしている状況だ。

尚、市販のプロセッサIP等との線引が難しいところではあるが、EDAの業界団体EDACの統計によると、EDA製品の一種としてカウントされるIPの販売額は増加傾向にあり、2012年上半期(1-6月)の売上合計は前年比9.8%増の8億1180万ドルとなっている。

この1年で報じたSynopsys,Cadence両社のIP分野関連のニュースは以下の通り。

Synopsys:

Cadence:

■Virtex-7が激化させるプロトタイピング市場

Xilinxがリリースした最新の28nmFPGA「Virtex-7」の登場により、今年はFPGAを搭載したプロトタイピング・ボードの市場で新製品のリリースが相次いだ。同市場の主な顔ぶれとしては、Dini Group、S2C、Synopsysなどが挙げられるが、今年は「Virtex-7」を機にProDesignとAldecの2社がプロトタイピング市場に参入した。ドイツのProDesignは元々プロトタイピング・ボードを手掛けていた企業で言わば復活デビュー。Aldecは論理シミュレーターの実績と同様にそのコストパフォーマンスの高さを武器にプロトタイピング・ボード市場に参入した形で、同社の強いアジアを中心にある程度のシェアを獲得していくものと思われる。

いずれのベンダの製品も今年リリースした新製品は、Xilinxの大規模FPGA「Virtex-7 2000T」を搭載しており、FPGAワンチップ当たり1200万ASICゲートのキャパシティを謳っているが、その拡張性やデバッグ容易性、コネクタやバス仕様によるパフォーマンス面において様々な独自性をアピールしている。

ボード以外のEDAツールも含め、この1年で報じたプロトタイピング関連のニュースは以下の通り。

■今年成長を遂げたEDAベンダ達

今年のEDA市場は大手3社の活況ばかりでなく、中小様々なEDAベンダがその業績を拡大させた。まず中堅どころの成長企業の筆頭と言えるのが、「Analog FastSPICE」を手掛けるBerkeley Design Automation。同社は今年も引き続き新規顧客の獲得を継続的に進め、そのシェアを拡大、現在同社の顧客数は125社にのぼると言われている。また、昨年2011年までの実績によるものだが、同社は今年、米国で有名なDeloitte社の北米成長企業ランキング「2012 Technology Fast 500」に選出された。2007年から2011年までの売上の成長率は302%だったという。Berkeley Design Automationは今年11月に新製品「Analog FastSPICE AMS」をリリースしており、同製品の投入で来年も更なる業績アップが期待できる。

検証関連では、フォーマル検証を手掛けるReal Intent、Jasper Design Automationが好調の様子だった。

Real Intentは、フォーマル・エンジンを用いたRTL設計の早期検証向けの「Acent」およびサインオフ検証向けの「Meridian」の2つの製品ファミリの展開で売上を伸ばし、2011年11月から2012年10月末までの会計年度の売上は、前年比倍増を達成というプレスリリースを発信。一部の情報によると同社の年間売上は約900万ドルでこの1年で顧客数を前年の1.6倍に増やしたという。尚、同社は今年、カリフォルニア州サニーベール市の地元優良企業に贈られる「2012 Best of Sunnyvale Award」を受賞している。

Jasper Design Automationは、大口顧客のARMとの取引を増やしたほか、今年はJuniper Networksも同社のフォーマル検証ツールを社内標準ツールとして採用した。また同社は今年、個別の検証問題に特化した目的別フォーマル検証ツール「JasperGold Appsをリリース。同製品のアプローチは、フォーマル検証導入の技術的、コスト的な敷居を下げ、早くも市場に受け入れられているようだ。尚、同社の社長兼CEOのKathryn Kranen女氏は、今年EDAの業界団体米EDACのチェアに選ばれた。

また、フォーマル検証関連では、OneSpin Solutionsも今年11月にMaximによる大型採用を獲得している。

その他、高位合成ツールの老舗Forte Design Automationは、国内外で顧客を増やしそのシェアを拡大した様子。調査会社Gary Smith EDA社の調べでは、2011年の実績として高位合成ツールにおけるシェアで競合のCalypto社を抜き首位を獲得したとされている。他には、高速RTLフィジカル合成ツールのOasys Design SystemsがIntelおよびXilinxから出資を獲得。両社をはじめとする大手半導体数社が同社のツールを導入しているようだ。

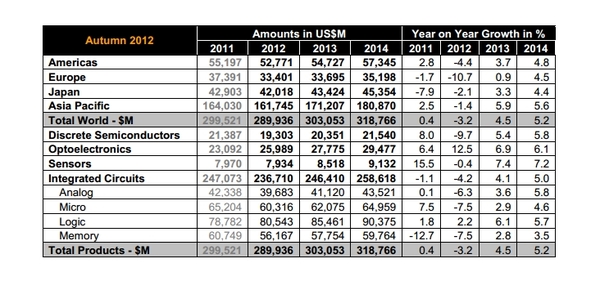

■世界半導体市場の動向

世界の半導体市場は、年始めのプラス成長予想に反して前年割れという結果となった。まだ現時点では11月、12月の売上統計は発表されていないが、10月までの累計売上額で前年比4.9%減となっており、WTSTの予測では2012年の世界半導体売上は前年比3.2%減の2899億ドルとされている。

※画像はWSTSのデータ

今年のマイナス成長は、欧州の経済不況、北米需要の冷え込み、メモリ価格の下落、PC向け半導体ニーズの減退など様々な要因が挙げられるが、モバイル端末や通信などの成長分野にフォーカスしたビジネスを展開するQualcomm、Broadcom、NXP、Nvidiaといったファブレス勢はいずれも好調で昨年よりも売上を伸ばした。また、ファウンドリ勢としても業界首位のTSMCとGlobalFoundriesは売上を大きく伸ばし、GlobalFoundriesはUMCを抜いて業界2位に上り詰めた。

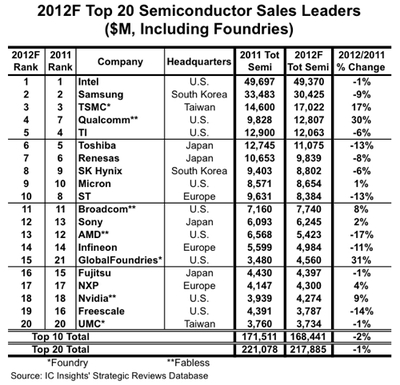

※画像はIC Insightsのデータ

※画像はIC Insightsのデータ現時点において各業界の調査機関は、2013年の世界半導体市場を3-6%の成長と予測しており、一部の調査機関は2016年までの平均成長率を7.4%と予測している。中でも強い成長が期待されているのは、モバイル端末や通信向け半導体、自動車向け半導体などで、その反面メモリやPC向け半導体に関しては需要の減退をささやく声もある。

尚、半導体関連の設備投資は今年をピークに来年は減少傾向にあり、強気のTSMCを除いて軒並み予算を削減する予定だという。

■国内半導体産業の危機

今年は言うまでもなく日本のエレクトロニクス産業にとって苦境の一年となった。大手家電メーカーの不振と合わせ、日本を代表する半導体企業エルピーダが倒れ、ルネサス エレクトロニクスが経営再建に追い込まれた。ここではあえてその詳細は記述しないが、今年、日本のエレクトロニクス産業の未来に不安を感じたという人も多い事だろう。

かつて家電や半導体で世界を席巻した日本にとって、今年の一連の出来事はショッキングな事実に違いないが、嘆いてばかりもいられない。時同じくして雪崩的に発生したこれらの出来事は、起こるべくして起きた事と捉えた方が自然で、これ以上同じ轍を踏まないためには、企業レベル、個人レベルで判断、行動する事が必要となるだろう。

では、どう行動すれば良いのだろうか?

その一つのヒントになるであろう、MITメディアラボ所長、伊藤穰一氏が様々なメディアや講演で口にしている有名な話をこの場を借りて紹介したい。

「これだけ世界が複雑になり、物事の変化のスピードが早くなると、もはや「地図」は役に立たなくなる。すなわち、予め用意された地図、じっくりと考えて綿密に作り込んだ地図をあてにしていては、目的に到達できないし、地図を作るためのコストも時間もかかってしまう。今必要とされるのは「地図」よりも「コンパス」で、方向性を捉えてすぐに進むことが重要。既成の地図を疑い自分で考えること、すなわち既成の権威や概念を疑う事が必要である。」

地図よりもコンパス。

今年も一年間ありがとうございました。

来年も引き続きEDA Expressをよろしくお願い致します。

コメント(1)

|ページの先頭へ|

地図よりコンパス。

良い表現ですが、じゃあコンパスの指し示す方向は誰が決めるのですか?

地図(マーケティング資料の事を指す)は、結構作成に時間がかかり、それから方向性(いわゆるコンパス)を決めるのが旧来のスタイル

コンパスの指し示す位置を探るには結局地図を頼りにしないといけない。実は良い言葉のようで、堂々巡りなフレーズに聞こえます。

前から、言われてる様に、日本人は即断即決が苦手。

動物的勘とまではいいませんが、市場を常に見ていて、即断即決出来るキーパーソンが必要とされてると思います。

そういうセンスのある経営者が半導体にいないのが問題。やはりそういう、経営者の教育も必要なのかと…