HOT TOPIX

中大竹内教授、ESLを駆使してハイブリッドSSDアーキテクチャとメモリ制御システムを開発

今年6月、ハワイで開催された「VLSI回路シンポジウム」にて、メモリ分野の研究開発で世界の先頭に立つ中央大学理工学部の竹内健教授のグループが、新たな「ハイブリッドSSDアーキテクチャ」とメモリ制御システムに関する発表を行った。

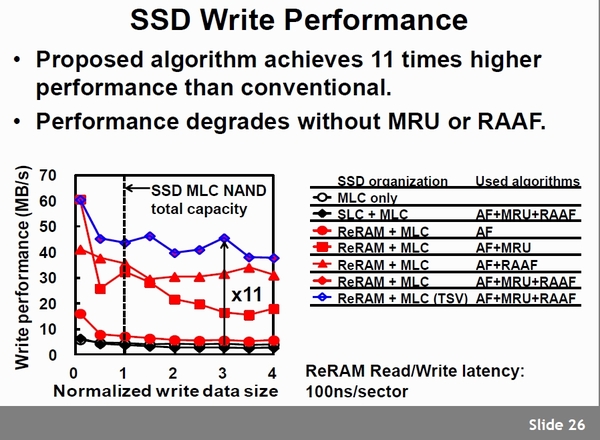

従来型SSDよりも11倍高速で消費電力は10分の1以下、寿命が7倍という「ハイブリッドSSDアーキテクチャ」の開発にあたり、竹内健教授のグループはSystemC TLMを用いたESL手法を活用したという。その詳細について竹内教授に話を聞いた。

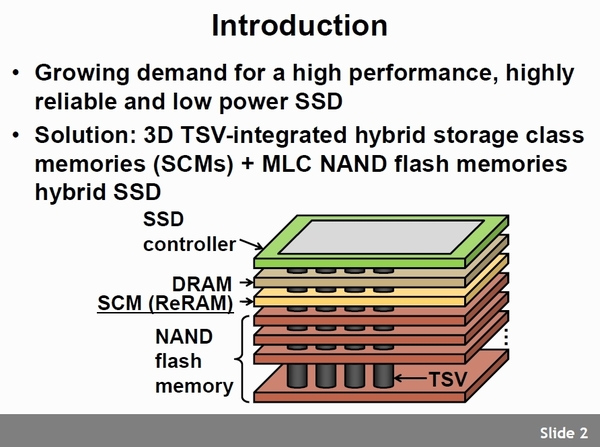

今回竹内教授のグループが行った「ハイブリッドSSDアーキテクチャ」の研究開発は、NEDOの委託事業「高速不揮発メモリ機能技術開発」として実施されたもので、次世代の高速メモリ「ReRAM(抵抗変化型メモリ)」とフラッシュメモリを組み合わせ、独自の制御アルゴリズムを用いる事でSSDのパフォーマンス向上と低消費電力化を実現するもの。

※画像は論文資料からの抜粋

従来、このようなシステムの開発はデバイスありきで行われるのが普通だが、今回のケースではReRAMを開発しながらシステム開発を進め、システムに対して求められるReRAMのあるべき仕様を抽出するというアプローチがとられており、「完全に動くチップが無い以上、エミュレーターでやるしかない」と、SystemC TLMモデルを用いたバーチャル・プラットフォームによって様々なシステム評価が行われた。一見縁遠いように思えるデバイス開発とSystemC/ESLが繋がる理由はそこにある。

しかし、竹内教授曰く、評価環境の立ち上げは容易ではなかった。今回の研究成果の発表までに約2年、うち評価を行うためのベースとなる環境の構築に約1年を要した。特に時間を要したのがコントローラーのモデル化で、ウェアレベリング、インターリービング、ECC(エラー訂正)など一般的なコントローラーの複数の機能をモデル化するのに最初の1年の大半を費やしたという。

こうした苦労の結果、コントローラーの他にメモリも含めたシステム全体がSystemC TLMベースでモデル化され、Synopsys社のバーチャル・プロトタイピング・ツール「Platform Architect」上でバーチャル・プラットフォームとして構築された。一部のモデルに関してはSynopsys側から提供されたものもあるが、メモリのモデルについては、インタフェースの条件やアクセス制約などのパラメーターを設定出来る簡易的なモデルを用意し、シミュレーション時には並行して進められていたデバイス開発側からの実測値を利用した。

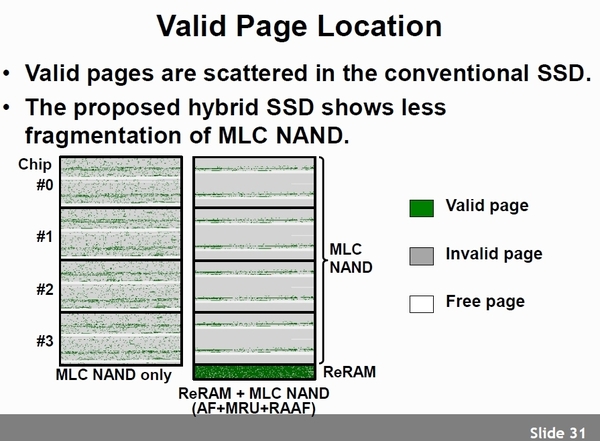

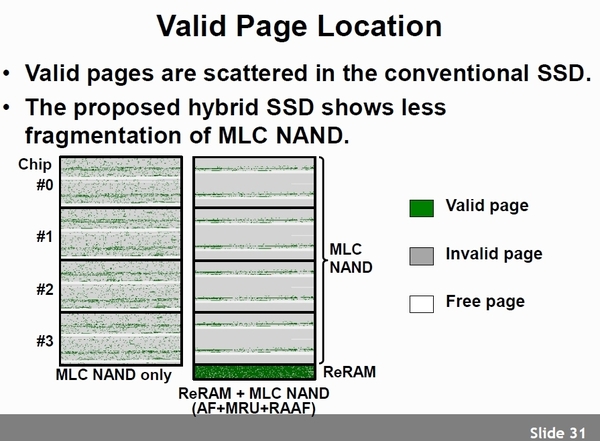

竹内教授のグループが開発した「ハイブリッドSSDアーキテクチャ」は、高速かつ低電力なReRAMを用いることで、細かなデータの取り扱いに不向きなフラッシュメモリのデメリットを解決するという発想で開発されたもので、独自に考案した3つの制御アルゴリスムによって、扱うデータの特性を見ながらReRAMとフラッシュメモリを使い分け、細かなデータや頻繁に書き換えるデータをReRAMに記憶することでフラッシュメモリの断片化を抑制する。

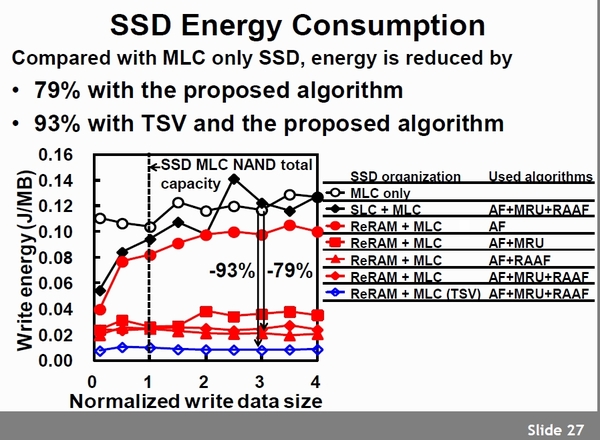

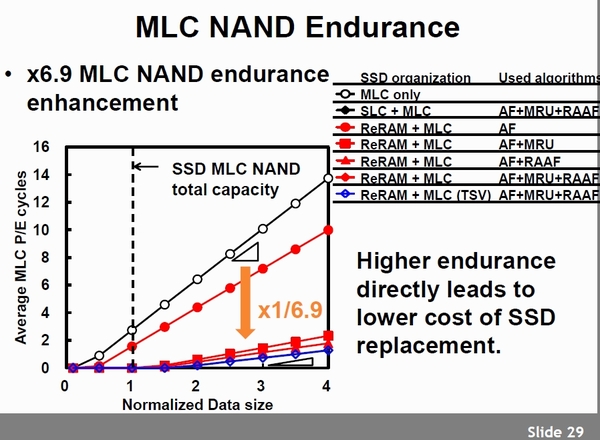

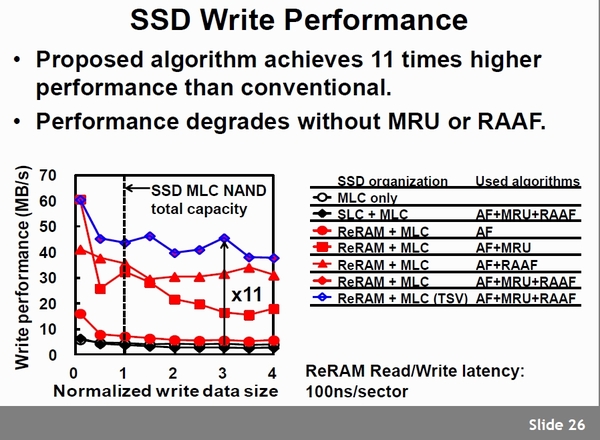

実際に構築したハイブリッドSSDのバーチャル・プラットフォーム上で、公開されている金融サーバー向けのアプリケーションをモチーフに3種類の制御アルゴリズムを試してみたところ、書き込み速度は最大11倍高速、消費電力は93%減、フラッシュメモリの書き換え回数は7分の1程度となり(いずれもTSVを用いた場合)、その有用性を証明することができた。竹内教授曰く、走らせるアプリケーション次第でその結果は大きく変わり、今回のケースでは細かいデータを多く扱うアプリケーションであったため、大きなメリットを得られたとの事。ただ、書き換え回数が7分の1程度で済んだという事はサーバーの交換頻度が7分の1となり、単品のReRAMが少々高くてもサーバー市場では十分なコストメリットを発揮するだろうという事だった。

※画像は論文資料からの抜粋

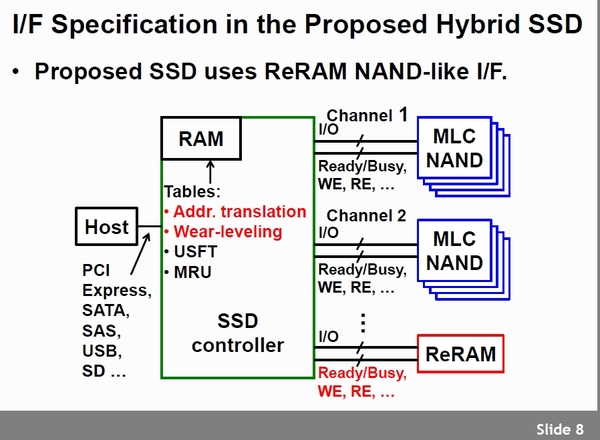

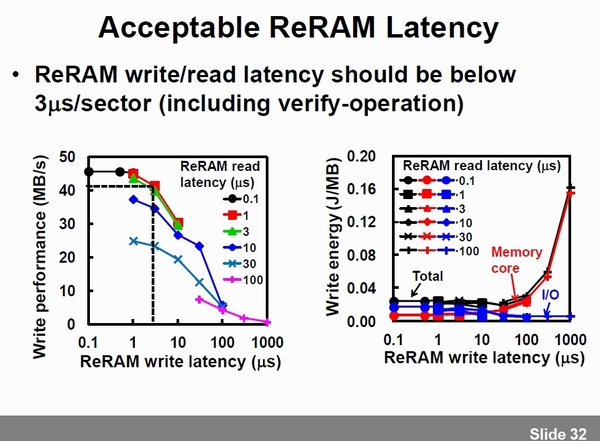

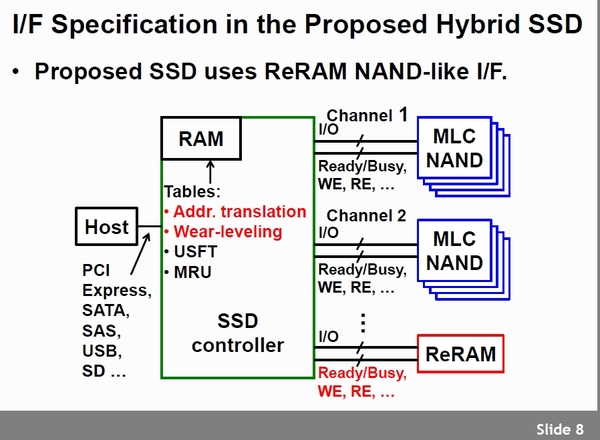

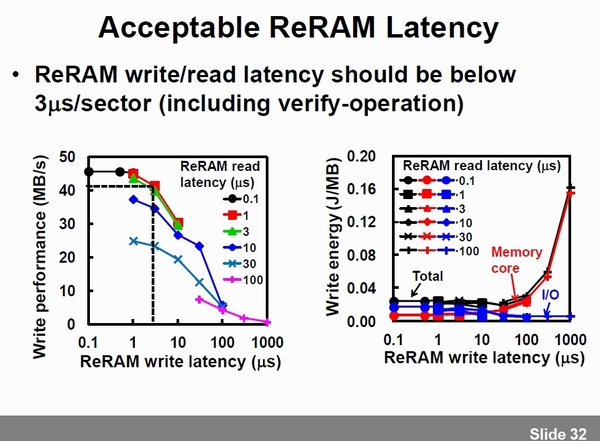

また、バーチャル・プラットフォームを用いたシミュレーションによって、ReRAMのインタフェースはDRAMのようなインタフェースよりも、NANDのようなReady/Busy式のインタフェースにした方が高速である点や、同システムにおけるReRAMのレイテンシは数マイクロ秒程度で問題無いという事を確認。目的としていたハードの仕様の抽出も実現することが出来た。

※画像は論文資料からの抜粋

竹内教授は、これらの成果はSystemC TLMモデルを用いたシミュレーションだからこそ成せる技で、更に評価データをビジュアル的に確認出来るなどESLを使うメリットは非常に大きいとコメント。世界的にもメモリ分野の研究開発でここまでモデルを用意してESLを駆使している例は無いだろうという事だった。

※画像は論文資料からの抜粋

※画像は論文資料からの抜粋

※画像は論文資料からの抜粋

※画像は論文資料からの抜粋尚、竹内教授は、SSDのパフォーマンスはアプリケーション次第だが、現実としてはアプリケーション開発側とストレージ(ハード)開発側には明確な切れ目があり、それが産業を分断していると指摘。そんな状況を踏まえ竹内教授のグループは、これからはストレージ側の事情とアプリケーション側の事情が分かっている者が勝つという頭で、現在世の中の様々なアプリケーションについて調査を進めており、次のステップとしてOSにまで踏み込んだ形でのシステムの最適化に取り組んでいるという。

|ページの先頭へ|