HOT TOPIX

Tezzaron社、3D IC設計事例:ツールフローとデザインソフトウェア Magma Design Automaton

Tezzaron社、3D IC設計事例:ツールフローとデザインソフトウェア

Magma Design Automaton

この業界における3D ICに対する興味は当然の如く拡大しており、3Dデバイスの設計方法は変化しています。通常の2Dツールフローは何年もかけて十分に成熟していますが、3Dデザインにおける重要な課題には対処しきれておりません。新しい3Dデザインプロセスは、この2Dデザインの従来の方法を少しずつ引き継いでいます。Tezzaron社が2003年に初の3D回路を設計したとき、設計者は一般的な2D CADツールを使用し、スクリプトによって3D DRC/LVSフローを補正しました。現在では、バックエンドフロー全体を処理するツールが揃っており、3Dデザインのパーティショニング、シンセシス、配置配線が可能になっています。

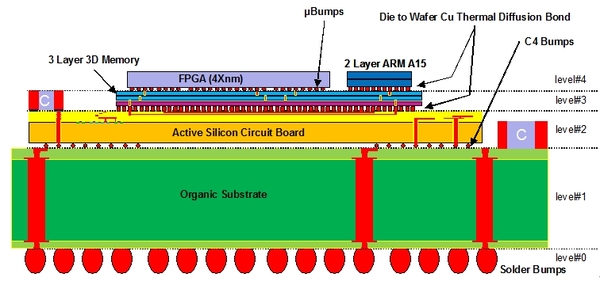

本稿では、3Dツール/ソフトウェアの現状や実用的なフローについて述べ、さらに改善が求められる分野について考察していきます。ここでは、Tezzaron社がパートナ数社とプロトタイピングを行っている次世代デバイスを例に進めます。例に挙げるデザインは、最先端ARM A15プロセッサ・スタック、市販のFPGAダイ、DRAMメモリ・スタックを使用しており、いずれも図1のとおりアクティブ・インポーザ上にアセンブルされています。

図1:サンプル・デバイス

■パーツ

ARM A15マイクロプロセッサは、ARM社のCortex-Aシリーズの最新版です。ARM A15マイクロプロセッサは、アウト オブ オーダ スーパースカラ パイプラインに加え、密結合された低レイテンシのレベル2キャッシュが組み込まれています。デザイン・インプリメンテーションを拡張するために、1階層から2階層までの処理をサポートできるマルチコア機能を利用することが可能です。3Dスタックの各階層には、コアが1つとそのL1キャッシュ、共有1MバイトL2キャッシュがあり、レイヤーをスタックしたまま拡張することができます。

FPGAは一般的な2Dデバイスで、ASICや他のロジックに適しており、このシステムの「繋ぎ」の役割を果たしています。

ここで使用されている3層の8GビットメモリであるDRAMは、Tezzaron社の次世代メモリです。このメモリは、このシステムのメイン・メモリです。

このシステムを構成する最後の要素は、アクティブ・インターポーザもしくはシリコン回路ボード(SiCB)です。信号の再送信後も、このシステムはシリコンを利用してパワーのレギュレーション、デカップリング、シグナル・ターミネーションを実行します。

■プロセッサ

3Dプロセッサは、ウェハ間のプロセスを利用し、フロントサイドからフロントサイドまでの結合ペアとして組み込まれます。ウェハからウェハまでを結合することにより、最小かつ高密度な垂直配線構造が可能になり、様々な方法でデザインの最適化を行うことができるようになります。ただし欠点として、KGDアプローチによるダイ間で行う歩留まり向上手法を実行することができません。全体的に、ウェハ対ウェハの3D設計は、全階層のトータル面積を見た場合、2Dとほぼ同等の歩留まりになります。

このサンプル・デバイスでは、3Dスタックの各階層にCPUコアを追加することにより、処理性能を拡張しています。これにより、パーティショニングの作業を軽減し、拡張機能を利用することで、より2Dデザインに近い形で設計を行うことが可能になります。初期段階で行った3D設計は、使用した3Dツールが8年前の古いものであったため、このような手法で行われました。この事例では、2Dデザインの3Dへの拡張は比較的強引に行われています。TSVや垂直配線プランニングは手作業で、合成や配置配線は 2Dで実行されています。けれども、より高機能かつ強力なフローに関して、別の手法を模索しています。

・パーティショニングと配置

A15は、Verilogデザインで提供されています。CPUは異なる数種類の方法でパーティショニングすることが可能です。例えば、CPUロジックを1つのレベルに配置し、キャッシュを別のレベルに配置することができます。この場合、キャッシュの製造プロセスを、CPUコアと統一することなく、異なるノードやテクノロジで実行することができます。プロセスの分割は、3Dインテグレーションの大きなメリットのひとつと言えます。

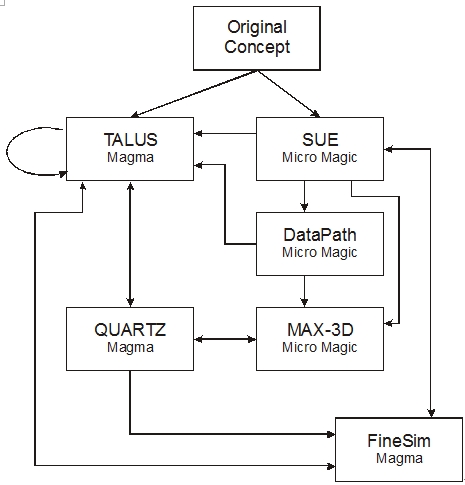

もうひとつの方法として、CPU内部に3Dに最適化された配置を行うことができる最新ツールの機能を利用することもできます。マグマ社のTalusを使用し、その柔軟な統合データモデルとTCLインターフェイスを利用した場合、Verilogを分割された領域に簡単に最適化することができます。このツール自体は現在3Dを考慮しませんが、フラットな2Dモデルに同一の領域を作成し、この領域同士をミラーリングする配線を定義することができます。つまり、ミラーリングによって3D配線を垂直に配列します。また、別の手法として、Talusを使用してフルブロックのフィジカル・シンセシス、早期パーティショニングを行い、.DEFファイルをMicro Magic社の3D配置ツールにインポートする方法もあります。Micro Magic社の3D配置ツールは、TSVを自動的にフロアプランに挿入し、TSVの配置を最適化し、セルのフロアプランをさらに最適化します。Micro Magic社の環境は、同社のMAX-3Dツールを使用することで正確な3Dフィジカル・エディッティングができるというメリットがあります。デザインは必要に応じて調整し、パーティショニングや配線前のクリティカルネットを改善することが可能です。Micro Magic社のツールで調整を行った後、再度データベースをマグマ社のTalus環境へ移行し、配線を行います。3Dでデザイン全体を分割することにより、性能を向上させ消費電力を削減することができます。理論的には、3Dは階層番号を表すNによって配線長を短縮することができます。これは非常に楽観的ですが、3D配線構造(face to faceあるいはTSV)が適切な精度である限り、意味のある結果になります。最長ネットはクロック、データ・バス、グローバル・コントロールで、いずれにも多くのリピータがあり、消費電力が大きくなります。このネットに3D配線を適用することにより、システムの速度や消費電力を簡単に30%から50%向上させることができます。

正確な3D配置の最適化はもちろん、各プロセスのコンセプトを考慮するツールが究極であると言えますが、今日、このようなツールはまだ見通しの段階でしかありません。

・配線

プロセッサの事例に戻りますが、上記を経て、パーティショニングは無事に実行され、初期配置が完了しています。配置されたデザインの垂直配線はスタンダードセル、あるいはフロックとしてモデル化されており、これらのモデルはラウタが配置された固有の3D配線を阻害しないように修正されています。必要に応じて、追加セルやブロックを浮動あるいは固定にすることができます。マグマ社のTalusラウタを使用して配線を終了します。現在、Talusラウタは「wormhole」接続のある一連の完了領域のみを確認します。この「wormhole」接続とは、明確な配線長がない一定領域間を接続する3D配線ポイントです。3D配線は、配線ネットワークに集中した固定要素としてモデル化されます。先に述べたように、垂直配線の位置は固定されますが、Talusは必要に応じて自由にセルやブロックのクラスタリングやバランシングの最終的な調整を行い、配線工程を完了させることができます。

・検証

デザイン検証には、デザイン・ルールチェック(DRC)とレイアウト対スケマティックの比較(LVS)があります。マグマ社のQuartzは、既に3D DRCとLVSデッキをサポートしており、2Dと3Dの設計条件を確認することができます。3D検証ツールは、使用されている複数のデータベースやテクノロジ・ファイルを同時にサポート、理解することができるかが鍵になります。Talusと同様に、Quartzは内蔵マルチデータベース機能を搭載しており、この基本条件を満たしています。既存のファウンダリ提供の2Dルール・デッキを簡易化し、再利用するために、デザインは2Dデザインとして処理され、各デザインに対して別々に確認、検証を行います。その後、全体を2Dデザインの3Dアッセンブリとして確認します。一般的に、3Dルール・セットは3Dアッセンブリ・ハウスが提供します。

・DRC

前述のとおり、3D DRCは各ファウンダリが提供するDRCデッキを使用して、各2D階層を初めて確認するときに実行します。純正のファウンダリ・デッキを使用することが重要になります。3Dで使用するためにデッキを大幅にカスタマイズした場合、継続的なメンテナンスやファウンダリからの補正に伴い、このデッキの更新作業を永遠に続けなければならなくなります。エラー結果は、3Dスタックで各シリコン階層に対して別々に生成されます。

2D DRC処理が完了した後、3D DRCを実行しています。QuartzへのTCLインターフェイスにより、3Dアッセンブリ・ハウスが提供する簡単なスクリプトで全ての2D階層を確認することができ、その後同様に3Dルールを処理します。3D DRCは、ボンディングやバックサイド・メタルと同様に、各2D階層のトップとボトム、ならびに各階層間の接続に注意を払う必要があります。場合によっては、3D DRCも実行して階層の3D接続の特定部分を確認します。例えば、TSVはファウンダリが提供する2Dルールにはない可能性もあります。微妙な差異で重要になるのは、同一のGDS階層が存在するシリコン階層と、存在しないシリコン階層が複数あるという点です。Micro Magic社のMAX-3Dは、3Dテックファイルの一部として3D階層のスタックアップに独自のGDS番号を指定することができます。このように、シリコンの第1階層のmetal1を第2階層、第3階層等のmetal1と区別することが可能です。

MAX-3Dで記述された3D GDSファイルには、デザインの確認に必要な全階層が含まれており、機械的にデザインを正確に製造することができます。3Dテックファイルと3D DRCファイルの記述やサポートは、3Dアッセンブリ・ハウス(この事例ではTezzaron社)によって行われます。

・LVS

Talusが、配置配線後のVerilogネットリストを提供しています。このネットリストは、シミュレーションやLVSのようなフィジカル検証に使用することができます。Quartz LVSはQuartz DRC同様、3Dで動作します。スクリプト・インターフェイスは、2Dネットリストに対して各2Dデザインを確認し、その後抽出された3D配線に対してトップレベルのネットリストを確認し、全体的な3D確認を行います。また、煩わしくエラーを起こしやすいルールの抽出や比較の再記述を行わなくて済むように、再びファウンダリが提供したオリジナルのLVSデッキを2D確認に使用することができます。3D LVSは、デバイスはなく、単なるピンのあるブロックとブロック間の配線があるだけで、非常にシンプルです。したがって、3D LVSデッキを生成するという3Dアッセンブリ・ハウスの作業を大幅に簡易化することができます。異なるテクノロジの2D階層を簡単に調整するために、3D LVSを使用することもできます。

■メモリ

メモリ設計は、プロセッサのフローと同様に行いますが、初期のデザインエントリーがVerilogである代わりに、キャプチャしたスケマティックを使用します。ここで使用するスケマティック・エントリーツールはMicro Magic社のSUEエディタです。このSUEエディタはMAX-3Dフィジカル・エディタと密接に結合しており、高ビットスライス志向のメモリ設計に便利なデータパス・コンパイル機能があります。マグマ社のツールと同様に、Micro Magic社のツールも広範囲でTCLを使用します。実際、Micro Magic社のツールの多くがTCLで記述されており、非常に導入がしやすくなっています。SUEエディタとMAX-3Dフィジカル・エディタを密接に組み合わせることにより、設計者からレイアウト・エンジニアへ情報を渡すことが可能になります。設計者は配置を行ったり、早期に遅延や物理的なサイズを見積もるために、スケマティック・エディタの後にDPCツールを使用することができます。メモリ・デザインの多くは適切な方法で組み合わされたパズルの欠片で構成されています。メモリ・セル自体がワードラインやビットラインのピッチを設定します。順にセンス・アンプやワードライン・ドライバのピッチを指示し、データパス要素のピッチも同様に設定します。

タイミング・ジェネレータとステート・マシンは複雑になりがちで、フライト制約の時間条件を満たしたり、回路遅延を一致させるために、非常に限定されたエリアに収める必要があります。レイアウト・エンジニアへの物理的な制約の説明が難しい場合があるため、レイアウト・エンジニアの問題に対する考えや、より良く動作するかもしれない代替的なインプリメンテーションに関する知識を設計者は取り入れることができません。経験上、このようにレイアウト・エンジニアが苦労して収束させなければならないような方法で、ほとんどのブロックが設計されているようです。設計者とレイアウト・エンジニアがより良い意思疎通を図るには膨大な時間が必要になり、さもなければデザインは最適とは程遠い結果に終ることになります。

・3Dフィジカル・エディッティングについて

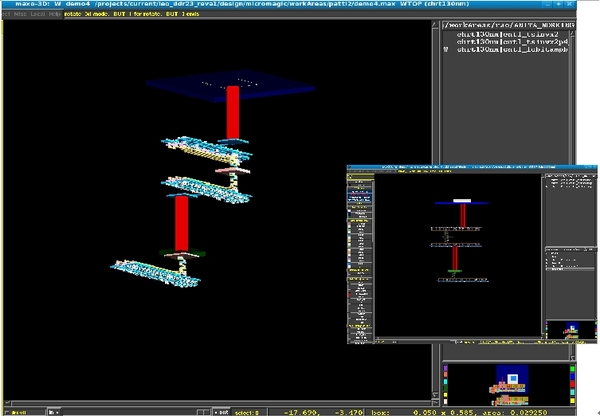

3Dデザインでは、フィジカル・エディッティングが非常に重要になります。MAX-3Dフィジカル・エディタは 真の3Dエディタで、エディッティング環境に異なるテクノロジ・ファイルを共存させることができます。2D階層を編集、もしくは3Dで異なる階層に渡ってカット・アンド・ペーストを行うことが可能です。このツールの長所は、実際の3D編集を行うと明らかです。2Dツールを使用した場合、単に3D接続を移動するにも異なるツールセッション、データ・マッピングでの編集や転送、外部でのDRC/LVSチェックが必要になります。MAX-3Dは基本的なDRC、LVS機能が搭載されており、3Dスタックアップ自体を直接表示します。

3D設計におけるもうひとつの必須要素として階層の指示があります。接続は、ある時はface to face、またある時はface to back、あるいはback to backになります。異なる階層を持つスタックの場合では、数百とは言わないまでも、数ダースの可能性が生じます。2Dツールを使用すると、3D設計は難しく、恐ろしいものになります。 優れた3Dツールは階層のトラックを維持し、3D接続を把握します。

・プロセスの分離

3Dメモリ・デバイスに戻りましょう。例に挙げている3D DRAMに対して、2種類の階層を設計、レイアウトする必要があります。Tezzaron社の3Dメモリは、2種類のプロセス・テクノロジで構成された2種類のウェハを使用しており、実際のところ製造メーカ2社で構築されています。このようにプロセスを分離させることにより、非常に高度な最適化、低消費電力で歩留まりの高いDRAM、高密度、SRAMに近い性能を実現することが可能です。製造の規模においても同様に、アレイの高い利用率と優れた歩留まりにより低コストを実現することができますが、本件に関しては別の機会にお話いたします。

メモリ・スタックのボトム階層はロジック・プロセスのテクノロジ・ウェハ、コントローラです。この階層には、センス・アンプ、I/Oインターフェイス回路、テスト/修復回路等、基本的にビットセルやサブ・ワードライン・ドライバ以外のメモリに含まれる全てがあります。この階層を構築するためにロジック・プロセスを使用することにより、より小型かつ小規模なレイアウト、高性能、場合によっては低操作電圧を実現することができます。

メモリ・セル階層は、高密度なビットセル、データ保存を実現するために、DRAMプロセスで構築しなければなりません。通常DRAMプロセスには多くの周辺設計ルール、高いデバイスの閾値、薄い酸化物があります。DRAMビットセルの 選択を行うには、内部電圧を上げる必要があります。さらに事実上全てのDRAMデバイスは、ビットセル選択のトランジスタ・リーケイジを削減するために、マイナス基板とワードライン・バイアスで駆動します。実際上の理由から、両階層を使用するために電圧ジェネレータを分割します。ロジック・プロセスは、優れたアナログ機能を実現し、チャージ・ポンプに迅速にフィードバックを行います。DRAMプロセスは高電圧で生成、操作を行うように設計されています。したがって、チャージ・ポンプの電源供給を行う高電圧回路部は、DRAM階層に適切に配置されます。

・デザイン・キャプチャ

メモリ・デバイスは、そのほとんどがスケマティック・キャプチャを行うことにより設計されています。これは、メモリ設計によってレイアウトを厳密に固定しなければならないという制限が生じるためです。メモリはボトムアップで設計され、メモリ・ブロックは基本的な構築ブロックとなります。サイズを最小化し、歩留まりや機能を最大化するために、メモリ・セルのレイアウトの最適化には数日ないし数週間がかかります。メモリ・セルを完成させた後、メモリ・セルが指定するピッチにドライバや検出回路を適合させます。高レベルの回路をメモリ・アレイ周辺に配置させます。デザインの各高レベル回路は、全体的なサイズにあまり影響を与えません。このボトムアップのアプローチは、スケマティック・ドリブン設計によってのみ行うことができます。

Micro Magic社のSUEエディタは、他のスケマティック・エディタと非常に似ていますが、情報をMAX-3Dに渡す機能があります。この機能は、レイアウトのイタレーション回数を削減するため、非常に重要です。さらにSUEには同じTCLインターフェイスがあり、ツール開発者が想定しないアドオンに対しても役立てることができます。Tezzaron社では、メモリ・デバイスに内蔵可能な約100万ビットという非常に大規模なバス幅を処理できる機能をいくつか追加しています。これには高性能な自動ラベリング機能が不可欠です。さらにあまり目立たないスケマティックの条件に、シミュレーションやLVSに必要なSPICEネットリストの生成があり、このネットリストのサブサーキットには数百万本のピンがあります。Tezzaron社の3Dメモリ・デバイスには、ロジック/コントローラ階層からDRAM階層をつなぐ200万以上の配線があります。すべてのスケマティック・エディタがこの多くのピンでネットリストを記述することができるわけではありませんが、SUEは記述することが可能です。

回路のエリアによっては、VerilogあるいはMMI Data path Compiler(DPC)を使用して生成されます。ここでは、あまり制限されることなく、絶対的なタイミングとフィジカル・レイアウトの双方を実装しますTalus 2Dフローでブロックの合成、配置配線を行った後に、Verilogフローを行います。TCLインターフェイスにより、メモリ内の多数のレイアウトでブロックを簡単にメッシュできるように、サイズ、形状、タイミング、配線層、方向等を制御することが可能です。

DPCフローは、SUEスケマティック・エディタの拡張機能です。SUE環境内でスケマティックはスタンダードセル・ライブラリからロジックゲートとして入力されます。Verilogシンセシス・ツールと非常に似た内蔵タイミング・アナライザがあり、見積もった長さやゲートの負荷を基にドライバ・サイズを調整します。ゲートは、スケマティックを使用してテンプレートとして 調整、配置されます。DPCスクリーンに切り替えることにより、実際の配置を表示し、ネストされた配線を確認します。これにより、設計者は繰り返し作業を行い、必要に応じて実際に確認したタイミング、サイズ、形状を基にデザインを改善することができます。DPCは様々なレベルを個々に最適化できるように、あるいは設計者の必要に応じてグローバルに対処できるように階層的に動作します。さらにDPCは非スタンダードセル・ブロックの配置も可能です。カスタム・アナログブロック、あるいは配線済みブロックをDPFライブラリに追加し、どこか周辺ではなく、プランの一部としてこれらのオブジェクトを組み込むことができます。最終的なDPC製品は、.defファイルになります。

・シミュレーション

メモリ・デバイスは巨大なアナログ回路であるため、SPICEで検証しなければなりません。Tezzaron社のDRAMデバイス独自の特徴として、プロセスの分離があります。複合デバイスのシミュレーションは、膨大なライブラリからデバイスを取り出さなければならない場合があります。様々なライブラリの中から独自のデバイス名を取り出すには注意が必要です。さらに、3Dデザインの非常に膨大なシナリオを検証できるように、シミュレータには大規模なデバイス容量が求められます。完成されたDRAMには、数十億のデバイスがあります。小規模な部分であっても、シミュレーションは数百万から数千万のトランジスタを処理しなければなりません。一般的に、メモリや3Dデザインには、トランジスタ・レベルのSPICEシミュレータが必要になります。SPICEデータは、設計が完了した時点で最小の共通標準になります。3Dアッセンブリの電圧のばらつきや温度向上効果がモデル化された場合、SPICE環境だけが必要とされる細密度や精度を提供することができます。マグマ社のFineSim Proは、シミュレーションをするメモリサイズを制御すると同時に、膨大なプロセッサのシミュレーションを行うことができる数少ないシミュレータのひとつです。

■FPGA

これは、ダイ形式で市販されているデバイスです。デザイン全体に対するブラックボックスとして扱われており、PCBデザイン用に処理されるパッケージとして使用されました。ダイレベルの統合には、KGDの取得や必要とされるフィジカル・インターフェイスのデータ等、新たな課題がありますが、低消費電力3Dデザインに関するこの情報を採用することで、標準的なMCMよりも新しい問題ははるかに少なくなります。もしFPGAが数十ワット消失した場合、実際に熱問題や電源供給に問題やリスクが増大するかもしれませんが、ここで例示しているデバイスの設定では発生していません。

■シリコン回路ボード

SiCBはこのデバイスでは受動的というよりも能動的に動作します。多くの企業が、パワー・レギュレータのような付加価値を利用することにより、インターポーザーやSiCBに将来的な可能性を感じています。インターポーザーが単なるファンアウト機能しか提供しなければ、市場は小さいままでしょう。有機基盤メーカは各々の製品を改善し続けており、少なくとも現在のガラスやシリコンと同等に近い性能を達成すると考えられます。しかし、トランジスタ、内蔵デカップリング・キャパシタ、ターミネーション・レジスタ、インターフェイス・バッファ、場合によっては光学機器の場合は、シリコンが唯一のソリューションとなります。このような機能を追加することにより、インターポーザーへのシリコン採用が真の価値を発揮することになり、他のIC機器の導入が不要になります。

このマルチコアCPUの電力を最適化するために、最適化された電圧と周波数で各コアやキャッシュを操作します。動作に伴う負荷が非常に軽く、おそらく単一コアで、わずか数十メガヘルツで動作が可能です。このアクティブCPUは、スタティック状態を維持する分だけの低電圧でCPUを停止させながら、閾値ぎりぎりで操作することができます。負荷が大きい状態では、全てのコアを動作させることはできるかもしれませんが、プロセスのばらつきが生じ、1CPUに対して最適な電圧でも、他のCPUには最適な電圧を供給することができません。パワーを最大化するために、負荷電力のレギュレーション・テクニックに近似した値を使用します。近似値と電源供給数は、この例では約20以上で、実際にはローカルのマルチチャネル・スマートパワー機器を使用するように指示しています。シリコン回路ボード(SiCB)はパワー・レギュレーション回路にとって理想的です。採用されているトランジスタ・プロセス・テクノロジは大規模ジオメトリで、非常に高い歩留まりを実現することができ、多くの要素で構成されたシリコンにとって重要になります。さらに、大規模なジオメトリ・テクノロジは、高電圧の入力にも対応することができ、アッセンブリを行う際の電流フローを削減しながらレギュレータの切り替えを行ったり、全体的なシステム・デザインのプリント基板や他の部分を簡易化することが可能です。

また、SiCBには高誘電率材料で構築されたバルク・キャパシタとトレンチングがあり、付随するICに数十マイクロ・ファッドのデカップリングを提供します。付随する個々のキャパシタを使用するためにスィッチング・パワーを利用し、効率やフォームファクターを最適化します。

最後に、SiCBにはポリシリコン・レジスタがあり、システムからの高速クロック配線を繋ぎます。ダイナミック・インピーダンス・マッチング回路が終端ネットワークを調整し、オーバーシュートやアンダーシュートなしで、最大のクロック振れ幅を実現します。

・デザイン・キャプチャ

SiCB向けのデザイン・パラメータやデザイン・ルールにより、プリント基板やチップに使用されるパラメータやルール間を緊密化しなければならないというツール条件があります。このローカルパワー・レギュレータで使用されているトランジスタには、的確なチップ・ツールが必要です。

私たちは、パッド配置やクリティカルネットの配線にMAX-3Dを使用しようとしたように、このデザインのキャプチャにMicro Magic社のSUEエディタを使用しました。さらに、レイアウト・エンジニアが、ネットが信号かパワーか、アナログかデジタルか等を理解できるように、ネット情報をSUEに認識させることができます。先にメモリ・デザインで図示したように、デザインを確認する際に、不測の問題を回避するのと同様に、イタレーションを削減することができます。

・フィジカル・デザイン

ここで再び、フィジカル・エディタとしてMAX-3Dを使用します。このツールにはTSVやバックサイド・メタルのような3D要素をサポートするために必要なフックがあります。さらに、高速信号やシグナル・インテグリティを確認するために必須な機能も搭載しています。MAX-3Dは、回路のトレースで使用するGDSを抽出し、3Dをカットします。さらに、シグナル・インテグリティ解析を行うために、定義可能なハローの使用や隣接構造の取り込みが可能です。図1で示された全体的な3Dシリコン・スタックのレベル2、3、4を、MAX-3D内で同時に複製、解析、編集することが可能です。

・検証とシミュレーション

検証、シミュレーション・フローは、すでに述べたフローと同様です。SiCBには、トランジスタ、レジスタ、キャパシタ・モデルはもちろん、独自のDRVとLVSのデッキがあります。これは全く別のシリコン回路になります。ワイヤ長の最大化や、他の機械的ストレス管理に関する重要な新しいルールがありますが、これらは最終的には追加デザイン・ルールになります。FineSimは膨大なデバイス容量と優れた性能を備えているため、再びシミュレーション・ツールとして採用しています。

■最終トップレベル・デザイン

・スケマティック

トップレベル3Dアッセンブリのスケマティック・キャプチャを実行するために、MAX-3Dエディタへのメッセージ・パッシング機能があるMicro Magic社のSUEを再び使用します。他のスケマティック・エントリーツールではなくSUEを選択することが重要です。しかし、他の部分がSUEを使用してエントリーされているため、設計のネットリストの多くがトランジスタ・レベルで生成されます。ネットリストは、Talusの合成済の階層やベンダーが提供するFPGA用Verilogモデルに添付することができます。

・フィジカル・デザイン

MAX-3Dは、ここでは最終的な3Dデザインで使用されます。メモリに実装された追加のバックサイド階層は、メモリ・デバイスレベルで追加されなければ、このトップレベルで追加することができます。最後の段階で、完成したデザインを確認し、内蔵されたDRC、LVS機能を使用してファーストレベルの検証を行うことができます。3D可視化機能により、最終的な3Dデバイスのアッセンブリを実際に確認します。全体的なアッセンブリに必要なデータベースは膨大で、簡単に100ギガバイトに達してしまう点に注意しなければなりません。この規模のデータベースに対応できるフィジカル・エディタはあまりありません。

MAX-3Dは詳細なシグナル・インテグリティ解析に影響を与える信号を切り取り、必要なGDSファイル全てを生成し、最終的なサインオフDRCやLVSの確認を実行するために表示することができます。

・検証

最終的な3Dアッセンブリは、グローバルなデザイン・ルールに忠実でなければならず、また、確実にマニュファクチャビリティを確認しなければなりません。3Dデザインルール・チェックには、3Dアッセンブリ・ハウス(この事例ではTezzaron社)が提供するテクノロジ・ファイルを使用します。デザインをチェックする上で最も現実的な方法は、フィジカル・インターフェイスやエレクトリカル・インターフェイスだけに接続されている個々のデバイスを理解するという方法です。この方法は、基本的にプリント基板のアプローチと同じです。必要に応じて、トランジスタまでの工程全てを検証することができますが、この事例ではあまりメリットがありません。

SUEで使用される適切なモデル・ステートメントを利用して、3Dネットリストで3D配線パスを確認するために必要な検証を行います。次に、必要に応じてMAX-3Dが必要なGDSファイルをトップ、ボトム・メタルのみのブラックボックスとなっている各シリコン層に生成します。さらにMAX-3Dは、3Dの位置情報等を確認するために、余分なデータを使用してGDSを生成します。バックサイド・メモリパッドはフロントサイドCPUパッドとラインアップされていますか?ファイル生成は、3Dアッセンブリ・ハウスが提供するテックファイルで指示されます。今日の3Dテックファイルは、即座にアッセンブル可能なファイルとして生成されますが、将来的にはデザイン・コントロール・ファイルにまとめることができるツールが出てくると予想しています。3Dテックファイルには、3Dアッセンブリ・ハウスの様々な機能がまとめられています。ダイ対ダイ、ダイ対ウェハ、ウェハ対ウェハ、フリップチップ、ワイヤ・ボンディング・テクニックは、全てこのような新しい3Dシステムに関与しています。今日、この情報を網羅するスタンダード・フォーマットはありません。

生成されたGDSファイルと手持ちのネットリストを使用して、再びQuartzで3D検証作業を行います。3Dチップ自体で実行しますが、スケマティック・ブラックボックスに対して部分ごとに新しい完全な3Dシリコン・アッセンブリをチェックし、全てのピンが考慮されており、フットプリントの位置が正確であることを確認します。その後、生成されたSUEネットリストを通じてトップレベル・スケマティックに対する3Dアッセンブリ全体をチェックします。その後、スタックでフィジカル3D接続をDRCするためにQuartzを使用します。さらに、Quartzを使用してERC、DFM、シグナル・インテグリティ・チェック、IRドロップ解析を行うことも可能です。他のスタンダロン・ツールは、最終的な検証の一環として、GDS情報やQuartz抽出データを使用して利用することができます。

・その他の3Dツール

R3Logic社のR3IntegratorはTezzaron 3D環境で初めて使用され、非常に有望視されています。このツールは、新たにパス検出やアップフロント・デザインのパーティショニング機能を提供しています。このツールを使用することにより、TSVの配置の際にトレードオフや補助作業が可能になります。図1のレベル0やレベル1で示されているとおり、有機基盤やパッケージングに利用できるように設定されています。R3Integratorは GDSフォーマットやmicronsのICと、GerbersやmilsのPCB双方のデータに対応、複製することが可能です。Micro Magic社のフィジカル・ツールと同様に、R3Integratorは3D設計や3D解析に対応するように開発されています。R3IntegratorはTSVがトランジスタを経由すべきではないTSV等の特性や使用を把握します。私たちは、Tezzaron社が既にサポートしているこのツールを基本フローに加えることを検討しています。

・部分損失

3D-ICデザインツールを討論する上で検討しなければならないことに部分損失があります。ここで述べている3Dフローは、間違いなく問題なく動作します。Tezzaron社は、このフローを数ダースもの顧客向けデザインはもちろん、多くの自社デバイスを製造するために使用しています。ここで使用しているPDKは、膨大な他のツールやフローと同様、このフローをサポートしているGlobalFoundries社130nmプロセスを基にした第8世代になります。しかし、このフローには依然としてギャップが残っており、アプリケーションに多少の影響を受けます。

・サーマル・モデリング

一般的な懸案事項として、3D設計におけるサーマル・モデリングがあります。いくつかのフローを調べてみましたが、条件を満たすものはありませんでした。最高のサーマル・モデリング・ツールは、数百万ないし数十億のデバイスを3Dでモデリングしながら、デザインの電力使用やストラクチャの熱伝導能力を理解しなければなりません。このようなツールは開発段階にありますが、これまでのところ、依然として2D近似値や非常に注意深く設計を行うことで問題に対応しています。

今まで、Tezzaron社のデバイスには詳細なサーマル・モデリングは必要とされていませんでした。Tezzaron社は各約12ミクロンという非常に薄い層を使用しています。これにより、デバイスの熱問題全体を削減することができ、通常ダイ・スタックとヒート・シンク間のサーマル・インターフェイス素材のみを考慮するだけで十分です。ここで例として挙げられているデモ・デザインでは、プロセッサとFPGA双方が3Dスタックのトップにあり、ヒート・シンクに直接繋ぐことができます。これは、Tezzaron社の3Dデザインで最も多く見られるケースで、高性能デバイスはトップに配置され、その信号は他の階層(通常はメモリ)を通じて垂直に配線されています。Tezzaron社のメモリには、数万の余分なTSVがあり、基盤からその上部にスタックされた高性能ロジックにパワーや信号を配線することが可能です。トップへのメモリ配置は、他のデバイス階層とそのヒート・シンク間に熱障壁が存在する場合があり、非現実的です。

・TSVの圧迫

3Dにおける、もうひとつの懸案事項にローカル・トランジスタ上のTV圧迫の影響があります。シリコンとTSV間のTCE不一致が、この圧迫の根本原因です。銅素材のTSVの場合、SPICEモデルの破損を回避するために大きなキープアウト・ゾーンが必要であり、少なくともマッチングを変える必要があります。ツールを提供している企業数社は、モデリング作業を行い、圧迫の影響をシミュレーション環境へ移行させようとしています。もし、TSVのキープアウト・ゾーンを最小化することができたなら、この影響は周辺に設計するのではなく、正確にモデル化しなければなりません。

Tezzaron社は、同社の最新製品でTSVにタングステン素材を使用、サポートすることで、この圧迫問題の多くを回避しています。シリコンとタングステンのTCEの不一致は、シリコンと銅の場合のわずか数分の一です。タングステンは、ほぼ全てのTSVが引き起こす圧迫問題を軽減しますが、アプリケーションに制限があります。最も太いタングステンTSVは、約20umで、確固たるプロセス制限はありません。

・3Dシンセシス

究極の3Dシンセサイザは、まだ登場していません。このようなツールは、RTLコードを利用し、デザインスピード、消費電力、コストのトレードオフを行い、デザインを最も低コスト、低消費電力、高性能デバイスとなるように分割しなければなりません。これは何年も先になります。マグマ社の既存ツール・アーキテクチャは、これらの機能のいくつかを提供することができ、複数のテクノロジ・ファイルやデザイン・ルールを同時に処理することが可能です。Tezzaron社は、既存のTCLインターフェイスを使用して、このフローを動作させる初期作業を完了していますが、まだ第一段階に入ったばかりです。さらに、まず高度なパーティショニングを行うR3Integratorのようなパス検出ツールも必要になります。完全にパーティショニングを行うには、依然として手作業に大きく依存します。少なくとも今後数年の内に、3Dパーティショニングは厳しい作業になってくるでしょう。

・3Dテスト

3Dテストに関する条件や問題は、別の論文に記載いたします。3Dに対応するよう強化されたIEEE1500のような新しいスタンダードがいくつか登場しています。3Dストラクチャのテストを行う魔法はありません。テストにおける従来のメソドロジを強化するために、多くの基本的な作業を行わなければなりません。さらに、デバイスの修復や冗長性に対応するための新しいメソドロジやスタンダードが登場しています。

■まとめ

本稿では、コンセプトに現実感を持たせるために、使用されているツールに触れながら、3D設計について詳細に渡ってご紹介してまいりました。この複雑な3Dデバイスは、皆さんの電話やタブレットに来年使用されることはありませんが、今後数年以内に電話やタブレットに設計されることになります。この数年の内に、数ダースの様々な3D ICデザインや、数千ものデバイスが顧客に提供され、統合された最終製品として見ることになるでしょう。パッシブ・インターポーザーは少量ながら既に出荷されており、本当の3DICデザインは、来年には大量生産されることになるでしょう。

3D実装に対するツールチェーンは既に対応可能になっていますが、完全もしくは設計者が望むようなメインストリームにはまだなっていません。とはいえ、3Dデザイン数は累積されはじめており、利用可能な3Dツールは完成度を高め、改善されています。既存の2Dツールは通常のフロー要素として3Dパラダイムを利用し、迅速に3Dに採用されていくでしょう。パッケージングとIC間のラインは、3Dテクノロジが小規模、低消費電力、低コスト、高性能という共通目標に進むにつれ、事実上消失していきます。今後数年の内に、3Dデザインツールが強化され、精製され、ICデザインのメインストリームに採用されると考えています。

図2:現在の3Dデザインフロー

図3:MAX-3Dツールの直交表示

本記事に関するお問い合わせ先:

マグマ・デザイン・オートメーション株式会社

Business Developement

ディレクタ 石神英明

Email: ishigami@magma-da.com

Tel: 045-470-4533 (代表)

|ページの先頭へ|