HOT TOPIX

FPGAを使った柔軟な検証メソドロジの採用事例 SpringSoft社

FPGAを使った柔軟な検証メソドロジの採用事例 SpringSoft社System-on-chip(SoC)デザインでは、規模の拡大と複雑化が日々進んでいます。その中でも検証作業はSoC開発期間全体の約70%を占めており、開発期間短縮のボトルネックとなっています。検証コストを削減し、早期に検証を進められるようなソリューションに対して、非常に大きな関心が向けられています。

台湾工業技術研究院(ITRI)は、2011年のDesign Automation Conferenceで本課題に対してのケース・スタディーを発表します。このケース・スタディーでは、FPGAを高度に視覚化することにより、FPGAベース・プロトタイプ・ボードの検証効率を劇的に向上させる革新的なアプローチをご紹介します。このFPGAベースのSoC検証プラットフォームは、台湾電気業界でICデザインに関連する新しい技術やメソドロジの研究開発に携わるITRIが、有望な新しい領域であると関心を抱いているものです。

( http://www.dac.com/conference+program+user+track.aspx?event=132&topic=12)

ケース・スタディー: 高性能マルチメディアSoCプラットフォーム

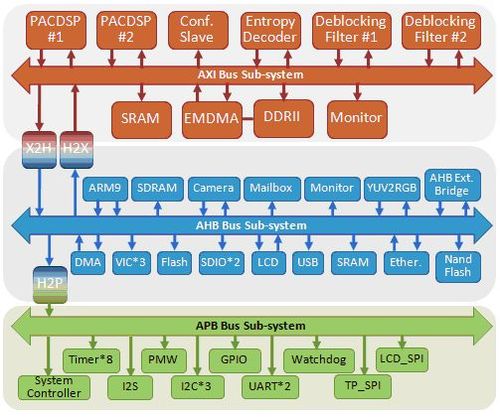

対象のSoCデザインは、高性能Android互換のマルチメディアSoCプラットフォームです。通信向けにはAXI、AHB、APBバスを採用しており、このAXIバスにITRIが設計した高性能カスタムIPを接続してH.264ビデオ・コーデックのようなマルチメディア・アプリケーションを高速化します。ARM、SDRAM、DMA、SRAM、イーサネット、LCDをはじめとするスタンダードIPは、通常のアプリケーション用としてAHBバスに接続されます。UART、タイマー、I2S、I2C、Watchdogのような低周波数IPブロックは、APBバスに接続されます。

従来のデバッグ手法では、FPGAプロトタイピング環境上でこのような問題をデバッグすることは非常に困難でした。FPGAに対する視覚化がわずかな信号やサイクルに限定されているため、問題を特定するために十分な情報を得ることができません。また、RTLシミュレーションで問題を解決するという方法も、OS(例:Linux)の起動に膨大な時間がかかるため現実的ではありません。また、この問題はソフトウェア、ハードウェア、もしくはドライバに起因している可能性もあるため、責任の所在を明らかにすることも難しくなっています。

異なるアプローチ

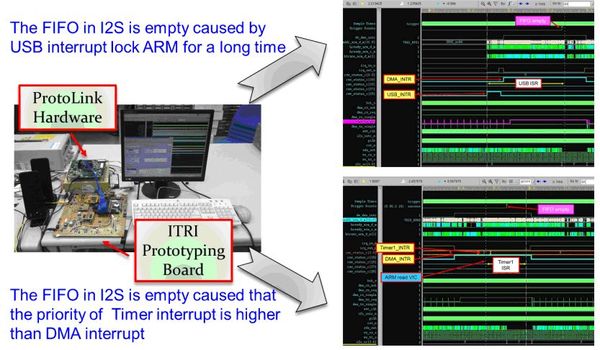

デバッグを容易化するためには、より効率的な検証メソドロジが必要です。当初、ITRIは自社のカスタム・プロトタイプボードが、SpringSoft社の新しいプロトタイプ検証環境「ProtoLink Probe Visualizer」に必要なインターフェイスに対応していないと考えていました。

簡単なテストをいくつか行った結果、SpringSoft社のエンジニアは、カスタムITRIプロトタイプボード上のスタンダードコネクタがProbe Visualizerソフトウェアが駆動するワークステーションとプロトタイプボードを繋ぐ上で問題なく使用できることを確認し、また、必要なサンプル・クロックを得るため、このボードに位相ロックループ(PLL)を追加しました。FPGAの設定プロセスは非常にわかりやすく、既存のスクリプトに統合して簡単に約100個の信号プローブを自動的に計測することができ、従来の手法と比較して6倍の視覚化を実現しました。FPGAリソースを使用することなく、外付けの2GB Probe Memoryに全プローブ・データを保存することができるため、追加されたプローブ・ロジックのオーバーヘッドはFPGAのわずか2パーセントと、比較的小さくなっています。また、外付けメモリには、ソフトウェア、ハードウェア、ドライバ間の関係性を明確に理解するために必要なサイクル長を保存する上で十分なデータ容量がありました。

ITRIチームは、SpringSoft社のVerdi™ Automated Debug Systemの最先端の視覚化、トレーシング、解析機能を利用し、プローブ・データを駆使してデバッグを行いました。複数回のデバッグ・イタレーションを行った結果、2つの問題点を発見しました。1つは、USBの割り込みがARMを長時間にわたってロックしたため、I2SのFIFOが空になり、問題を引き起こしていました。2つめの問題は、タイマー割り込みの優先順位がDMAの割り込みより高く設定されていたため、同様にI2SのFIFOが空になっていました。 ProtoLink Probe Visualizerを用いれば一般的なRTLでデバッグを行うことができるため、ITRIのエンジニアはデザインの動作を解析し、同じ症状を表しているにも関わらず2つの異なるシナリオに起因するこのようなバグの原因を迅速に特定することができました。

解析の結果、さらに別の信号を観測しなければならなくなりましたが、当初のプローブ・リストにはありませんでした。そこでITRIのエンジニアは、高速Probe ECO機能を使用して、デザイン全体を再コンパイルすることなく、わずか10分で10個の新しいプローブ信号を追加しました。RTLで新しい信号を指定し、デザインの合成・配置配線操作をやり直すために2時間から3時間かけていた従来のデバッグ手法と比べると、これは大きな時間の短縮になりました。

操作性に関しても、エンジニアはVerdi環境からProbe VisualizerにRTLで追加されたプローブ信号をただドラッグ・アンド・ドロップするだけでした。このシステムは自動的にRTLとゲートレベル間の信号の関連付けを行い、FPGAの配置配線ファイルに直接、迅速に部分的な配線を行うので、デバッグ時間を大幅に短縮することができ、短期間で複数のデバッグ・セッションを行うことができます。このデザインで使用されていた「ブラックボックス」IPブロックでさえ、EDIFの名前のみでプローブすることができました。

結果を評価する

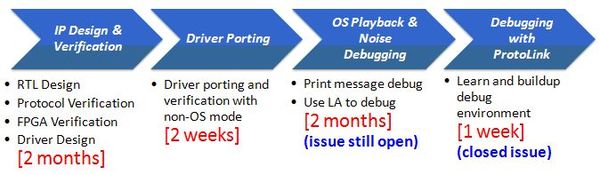

問題を修正し、デザインのテープアウトを達成した後、ITRIのエンジニアはこのプロジェクトに費やした実際の時間を計測し、新しいFPGAベースのSoCプロトタイプ検証メソドロジの結果を評価しました。

RTL設計、シミュレーション、プロトコル検証、FPGAインプリメンテーションに費やした時間は約2ヶ月でした。ドライバのポーティングと検証に費やした時間は、はるかに短く、わずか2週間でした。その後、FPGA内部の信号をチェックするためにハードウェア・ロジック・アナライザを使用してオーディオ問題の解決、問題の関連付けと検出を行うためにオーディオ・ドライバに観測ポイントを追加する作業に2ヶ月を費やしました。このハードウェアを用いたFPGAデバッグ・アプローチは、デザイン開発と同等の時間を費やしたものの結果を出すことができず、ITRIチームを大いに失望させました。しかし、1週間に渡るSpringSoft社からのトレーニングやサポートにより、ITRIのエンジニアはProtoLink Probe Visualizerを使用してから、わずか1週間で2つの問題点を明らかにすることができたのです!

まとめとして、SpringSoft社のProbe Visualizerは、機能豊富なリアルタイムのデザインの視覚化を実現し、従来のアプローチと比較してプロトタイプ・デバッグ時間を半減するため、ボード上でVerdiのデバッグ機能を利用できる革新的かつソフトウェア・ベースの手法を提供し、プロトタイプ検証に対するパラダイムを変革します。これにより、デバッグの生産性と全体的な検証効率を向上し、ITRIのような会社はSoC開発工程の早い段階でFPGAベースのプロトタイプを行い、最先端かつ非常に優れたFPGAテクノロジを搭載した次世代ボードに迅速に移行することが可能になりました。

筆者について

Howard Maoは、SpringSoft社のProtoLink製品ラインのシニア・ディレクタです。Howardは台湾、新竹のNational Chiao-Tung Universityの電子工学部で理学士号と修士号を取得しています。Email: howard_mao@springsoft.com

Vext ChenはITRIのデザインフロー開発部門の技術課長代理を務めています。Vextは台湾、台中のNational Chung-Hsing University、電子工学部で理学修士号を取得しています。Email: vext@itri.org.tw

|ページの先頭へ|