NEWS

Mentor Forum 2017 AlchipがHPCチップの大幅パワー削減に成功した訳

2017年9月29日、メンター・グラフィックス・ジャパンは、品川本社でセミナー「Mentor Forum 2017」を開催。同社Calypto事業部の製品である「SLEC」、「PowerPro」、「Catapult」の最新情報を披露した。

ここでは同セミナーで行われたAlchip社の古園 博幸氏によるローパワー設計ツール「PowerPro」の事例講演についてレポートする。

講演タイトル「先端ASICのローパワー設計 Alchip独自クロック手法とPowerProのコラボレーション事例」

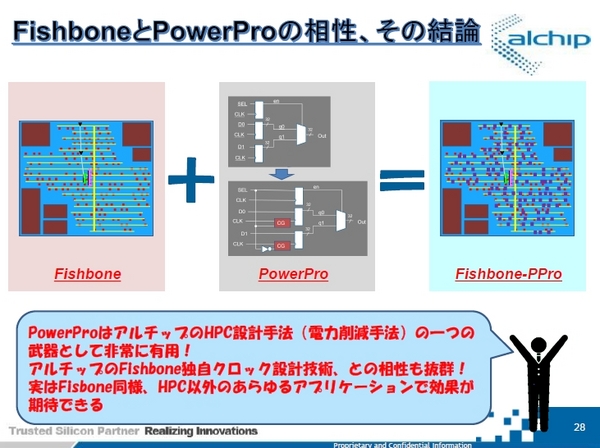

Alchipの古園氏の講演は、同社が力を注いでいるというHPC(high-performance computing)市場向けのチップ開発の話。同社の独自技術とMentorの「PowerPro」を組み合わせる事でHPCチップの大幅なパワー削減に成功したというものである。

※Alchip社 古園氏

古園氏によると、HPC向けのチップに求められる数々の技術要件の中でも特に重要なのが「電力あたりの性能」で、性能を保持しつついかに電力を最小化するかがキーとなっている。そこで同社はダイナミック・パワーの削減に向けて、独自の低電力クロック設計技術と「PowerPro」のクロック・ゲーティング及びメモリ・ゲーティングを組み合わせて使ってみる事にした。

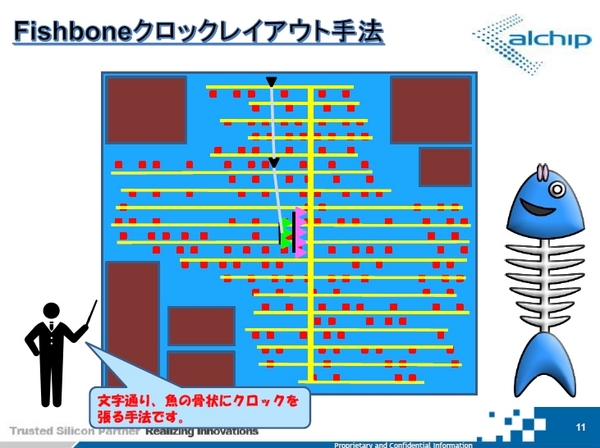

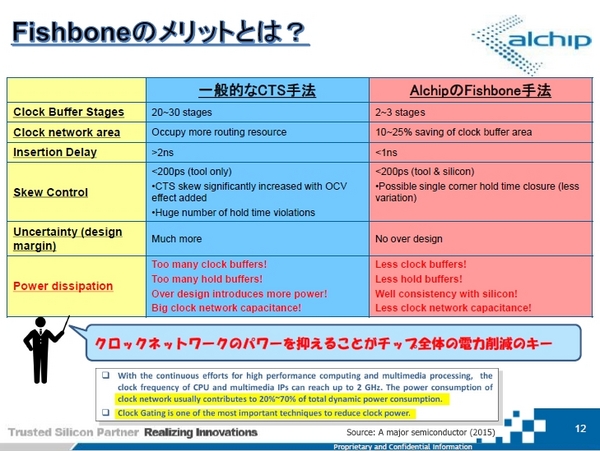

Alchip独自の低電力クロック設計技術とは、「Fishbone」と呼ぶ魚の骨状にクロックを張る独自のクロック・レイアウト手法の事で、マルチドライバを用いて全てのFFまでの段数を揃える事を基本としている。古園氏によると「Fishbone」手法は、一般的なクロックツリー・シンセシス手法よりもバッファの段数や配線領域、全体のレイテンシを抑える事が可能、すなわちクロック・ネットワークのパワーを抑える事が可能で、それがダイナミック・パワーの削減に大きな効果をもたらすという。

今回の試行にあたりAlchipはHPCチップの実デザイン(16nmプロセス,動作周波数600MHz)に対してまず「PowerPro」を実行してみた。その結果、「PowerPro」はFFのパワーで26%、メモリのパワーで80%削減可能というレポートを出力した。それを踏まえてAlchipの「Fishbone」手法でレイアウトを行ったところ、トータル・パワーを59%削減という驚くべき結果となった。古園氏曰く、大幅な仕様変更でも行わない限り通常これ程のパワー削減は不可能という事で、元々チップ全体で112Wと想定していたパワーを46Wまで削減する事に成功した。

想定外のパワー削減効果を分析したところ、「Fishbone」によるパワー削減効果が最も大きいのはクロック・ネットワークのパワー削減で一般的なクロックツリー・シンセシス手法よりもパワーを66-69%削減していた。一方「PowerPro」によるパワー削減効果はチップ全体のパワーに対して51-55%と大きな効果を発揮している事が分かった。この「PowerPro」の効果は同ツールのレポートとほぼ同等だったという。

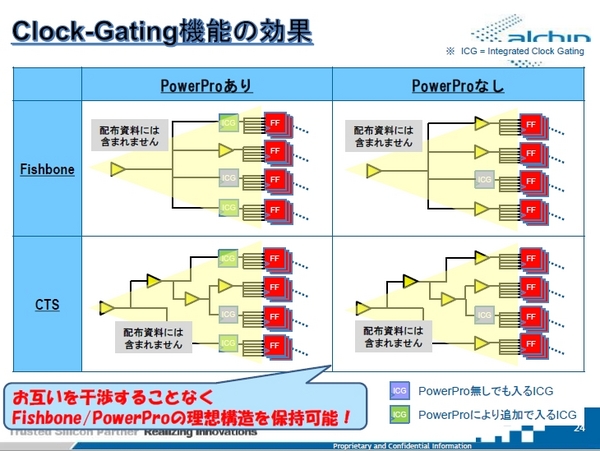

これらの結果に加え、更に「Fishbone」と「PowerPro」の効果を詳細に分析した結果、古園氏は「Fishbone」と「PowerPro」の相性は抜群で、お互いを干渉する事無くパワー削減効果を発揮できるという結論に至った。古園氏は同手法はHPCに限ったものではなく、様々なアプリケーションに適用可能と考えているという。

なお、Alchipでは今回の成功事例を受けて、今後積極的に「PowerPro」を活用したローパワー・デザイン・サービスを提供していく予定(7nmデザインにも適用可能)。メモリ・ゲーティング用のメモリモデルの作成や「PowerPro」を用いたECOレイアウトなどにも対応してくれるという話だ。

|ページの先頭へ|